基于FPGA的IEEE-1394b双向数据传输系统设计

3 软件工作流程

在NIOSII IDE集成环境下,根据1394 OHCI协议,使NIOSII处理器实现对总线的初始化,以及管理,并通过DMA方式实现等时和异步数据传输。其中等时数据传输仅考虑将外部视频数据打包发送到主机,而异步数据传输分为主机发起的异步传输和1394设备发起的异步传输。

3.1 系统的自举

主要为系统初始化、检测电缆以及根节点的确定。系统初始化主要是配置链路层芯片寄存器,使其工作在需要的状态下。分为对PCI寄存器的初始化和对OHCI寄存器的初始化。对PCI寄存器的初始化包括对TSB82AA2设备ID和PCI厂商ID的验证,OHCI基地址寄存器的设置以及对指令状态寄存器的配置。而对OHCI寄存器的初始化则包括对各个中断寄存器和DMA上下文的设置,以及控制寄存器的配置。检测电缆是否插入是通过读取物理层芯片某寄存器的相应位来判断的。电缆插入后,通过检查和配置Node ID寄存器,强制设置本节点为子节点,主机为根节点,直到成功为止。

3.2 数据的传输

在1394 OHCI中,不管是等时传输,还是异步传输,都是通过DMA方式实现的,而且每个DMA都有一个FIFO,用于暂时存放数据。其中各FIFO的存储容量为:异步发送(AT)FIFO为5 kB,异步接收(AR)F7FO为2 kB,等时发送(IT)fIFO为2 kB,等时接收(IR)FIFO为2 kB。无论是物理层接收到的还是要发送出去的数据包,都被暂时存放在相应的FIFO中,由1394套片的内部逻辑控制将其传送到1394总线上。

(1)主机发起的异步传输。

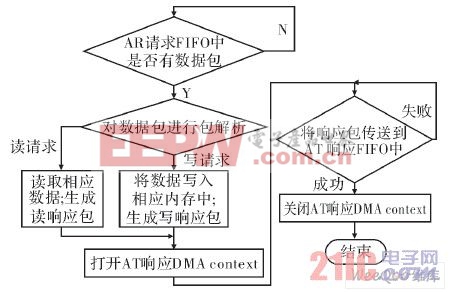

主机发起的异步传输即由主机发出异步传输请求,1394设备进行响应,因此在这一部分,主要是异步请求包的接收以及异步响应包的发送。其工作流程如图2所示。1394设备接收到主机发来的异步请求包后,就会产生异步接收请求中断,这可由链路层芯片中断寄存器的RQPkt位表征。当一个数据包传送完毕后,数据包的最后一个指令描述符的xferStatus字段将被重置,这时数据包已被成功传送到AT响应FIFO中。

图2 主机发起的异步传输工作流程

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码