AD9779A的寄存器配置及PLL频带优化

随着科学技术的发展,通信、测量等各个领域对信号源的要求越来越高,高速任意波形发生器成为市场的热点。高速DAC作为任意波形发生器的关键部分,其性能对高速信号有着极大的影响。AD9779A是目前国内能买到的性能较高的高速DAC芯片,内部集成PLL倍频电路、同步控制、增益控制等功能模块,通过SPI接口和外部通信,可以设置优化各种功能以达到最佳性能。

1 AD9779A简介

AD9779A是Analog Devices公司生产的双通道16位高速宽动态范围数DAC,采样率1Gsps,允许高至奈奎斯特频率的多载波生成。0.18μm CMOS工艺制作,工作电压1.8~3.3 V,采样率1 Gsps时功耗1 W,具有高速、低功耗的特点。AD9779A还包含低噪声高性能的PLL时钟倍频电路,可以减轻板级时钟输入的负担。AD9779A可以应用在无线基础设施(WCDMA/CDMA2000/TD/GSM)、数字频率合成、宽带通信等领域。

2 AD9779A的SPI通信方式

2.1 AD9779A的SPI接口简介

SPI总线系统是一种同步串行外设接口,它可以使MCU与各种外围设备以串行方式进行通信,以交换信息。通过AD9779A的SPI接口可以配置内部的寄存器,设置各种功能以达到设计要求。AD9779A的SPI接口支持单字节或多字节传输,包括高位优先和低位优先格式,由4根线组成,分别是:

①串行时钟(SCLK),作为数据输入输出的同步时钟,最大时钟速率40 MHz。输入数据在时钟的上升沿锁存,下降沿数据输出。

②片选信号(CSB),低电平开始通信周期并保持到通信周期结束,高电平时SDO和SDIO为高阻态。

③串行数据输入/输出口(SDIO),该引脚既可作为单向数据输入口,也可作为双向数据输入输出口,通过寄存器(0x00,bit7)控制,默认为单向数据输入。

④串行数据输出(SDO),作为数据输出口,SDIO配置为双向端口时,SDO为高阻态。

内部配置的任何改变会在最后一位写入后立刻生效,因此,当有多个字节写入到寄存器中时可以在一个通信周期中改变配置。同时,为了预防意外情况,改变寄存器配置时推荐使用单字节传输。

2.2 SPI接口操作

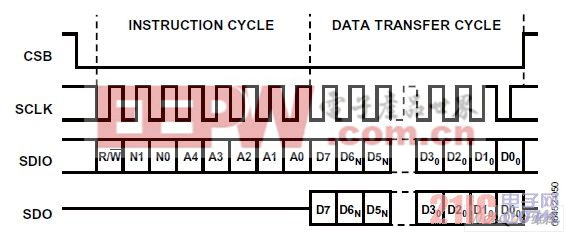

AD9779A的一个通信周期包括两个阶段。

第一阶段是指令周期(向设备写指令)与前8个SCLK的上升沿一致。指令字节规定串口控制器数据周期,也就是通信周期第二阶段的数据传输是读还是写,数据传输的字节数和第一个寄存器的地址。每个通信周期的前8个SCLK上升沿用来向设备写指令字节。

剩余的SCLK是通信周期的第二阶段。第二阶段是设备与MCU实际的数据传输阶段。每次可以传输1~4个字节,传输的字节数由指令周期决定。寄存器在每个字节的最后一位写入后立刻改变。

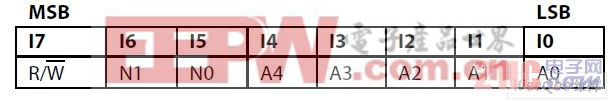

SPI指令如表1所列。

表1 SPI指令

,决定是读操作还是写操作。逻辑1读操作。逻辑0写操作。

N1和N0决定数据传输周期中传输的字节数。N1、N0表示的字节数如表2所列。

表2 N1、N0表示的字节数

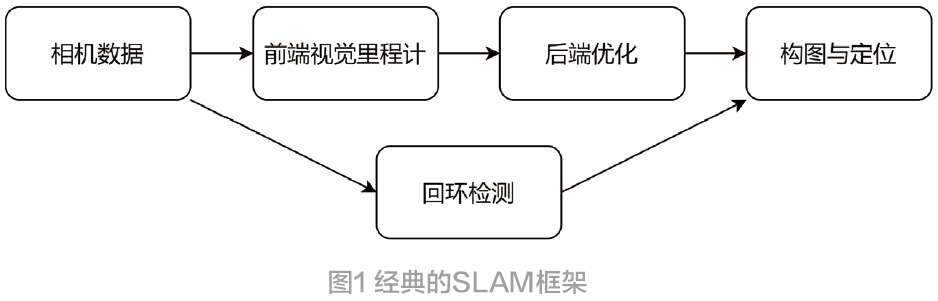

A4~A0确定在数据传输时哪个寄存器可以被访问。在多字节传输时,这个地址是起始字节地址,其余寄存器地址由器件自动产生。最高位优先的寄存器配置时序如图1所示。

图1 最高位优先的寄存器配置时序如图

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码