一种AES密码算法的硬件实现

0 引言

密码模块是安全保密系统的重要组成部分,其核心任务就是加/解密数据。目前,分组密码算法AES以其高效率、低开销、实现简单等特点被广泛应用于密码模块的研制。随着计算机信息技术和超大规模集成电路技术的成熟与发展,通过硬件来实现密钥模块的内部运作,可保证在外界无密钥的明文流动,能够实现真正意义上的保密。此外,硬件实现还具有高速、高可靠性等特点。目前许多AES算法的硬件实现采用基于RAM查找表方式来实现算法中最关键的SubBytes部分。本文采用复合域来实现SubBytes部分的求逆运算,以便于采用组合逻辑减小面积。同时采用加/解密运算中列变换的部分电路进行复用,从而进一步节省实现面积。这样可以使AES密码应用于RFID系统,IC卡等面积要求较小的场合。

1 AES算法简介

AES算法是一种迭代型分组密码,其分组长度和密钥长度均可变,各自可以独立指定为128 b,192 b,256 b。本文主要讨论分组长度和密钥长度为128 b的情况。AES算法是将输入的明文(或密文)分成16个字节,在第一个Add Round Keys变换后进入10轮迭代。迭代过程的前9轮完全相同,依次经过字节代替(substitute bytes)、行移位(shift rows)、列混合(mixcolumns)、轮密钥加(add round keys),最后一轮则跳过了列混合(mix columns)。解密过程与加密过程类似,但执行顺序与描述内容有所不同,因此AES算法的加解密运算需要分别实现。

2 AES算法的硬件设计

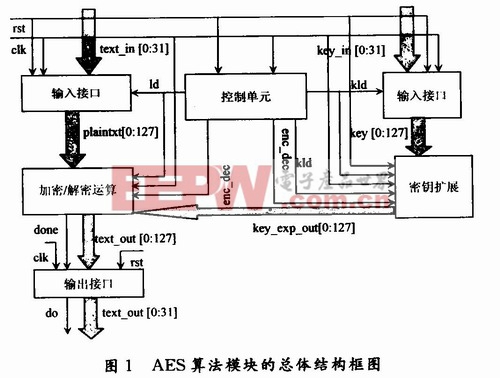

根据AES算法的原理和基本结构,将整个AES算法模块分成4个相对独立的子模块:接口模块、控制单元模块、加解密运算模块、密钥扩展模块。本文所设计的密码算法不包括密钥发生器,所用的密钥通过接口模块由外部输入,加解密运算后的数据经输出接口输出。AES算法模块的总体结构如图1所示。

2.1 接口模块的设计

输入接口模块的主要任务是:将数据传送到加解密运算模块,将外部输入的密钥传送到密钥扩展模块。由于明文和密钥输入都是128位,将导致整个模块的输入/输出过多,占用太多资源,考虑到本文的设计主要应用于对面积要求较小的场合使用,如RFID系统中数据的传输,即每次传输的数据是64位,故采用4个32位寄存器,在时钟的控制下每次输入1组32位,通过4个时钟周期可得到128位的数据,可以有效减少资源的占用。输出接口模块的作用是将128位的解密运算结果输出,同样也采取32位分4组输出的方法。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码