一种新型高精度CMOS带隙基准源的设计

3 仿真结果与分析

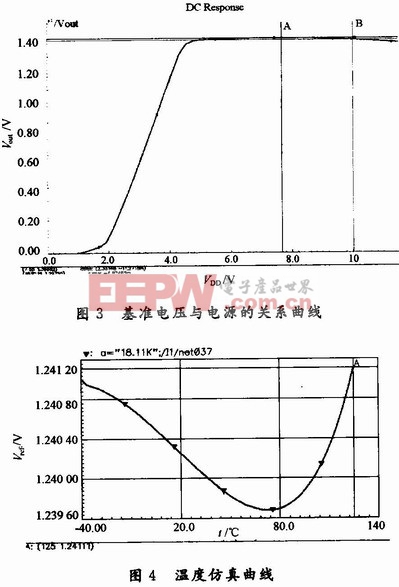

图3说明了该基准源对电压的抑制效果。根据仿真数据,在所取5~10 V的输出电压范围经计算基准电压电源抑制比为82 dB。图4为Cade-nce下的温度仿真曲线,根据所要求取的温度范围在-25~+120℃,计算得温度系数为:TCF=7.427 ppm/℃。图5为整体电路的版图设计,面积近似为0.022 mm2。

4 结语

本文通过对传统带隙基准源的基本原理分析,设计的基准电路工作电压为5~10 V,通过饱和状态MOS等效电阻对PTAT电流反馈补偿,得到了82 dB的电源电压抑制比和低于7.427 ppm/℃的温度系数,版图面积0.022 mm2。该电路产生的基准源电压基本满足普通应用要求。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码