简单数字钟仿真电路图大全(五款数字钟仿真电路图)

作者:fanxiaoxi

时间:2022-10-12

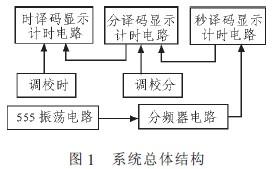

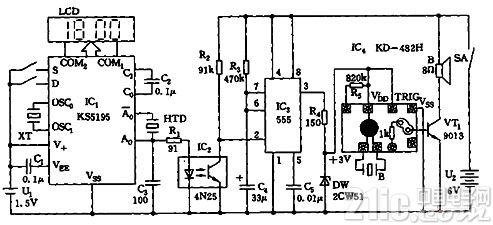

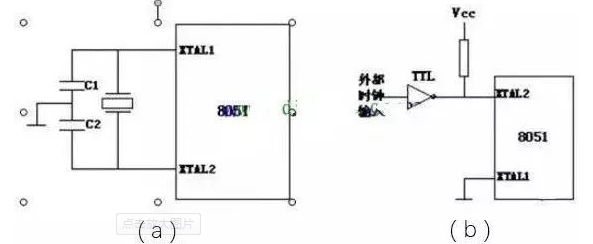

数字钟实际上是一个对标准频率(1HZ)进行计数的计数电路。由于计数的起始时间不可能与标准时间(如北京时间)一致,故需要在电路上加一个校时电路,同时标准的1HZ时间信号必须做到准确稳定。通常使用石英晶体振荡器电路构成数字钟。

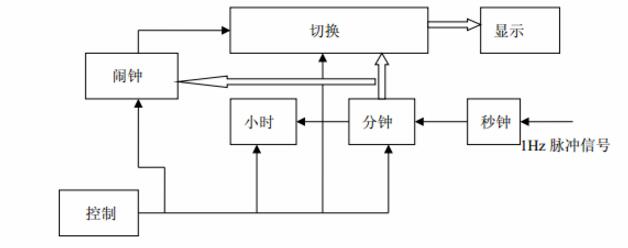

简单数字钟仿真电路图(一)

将时钟信号输给秒模块,秒模块的进位输给分模块,分模块进位输入给时模块,切换的时候使用2选1数据选择器进行切换,电路框图如下:

该方案的优点是模块内部简单,基本不需要额外的电路,但缺点也很明显,该方案结构不清晰,模块间关系混乱,模块外还需使用较多门电路,不利于功能扩充,且使用了异步电路,计数在59的时候,高一级马上进位,故本次设计不采用此方案。

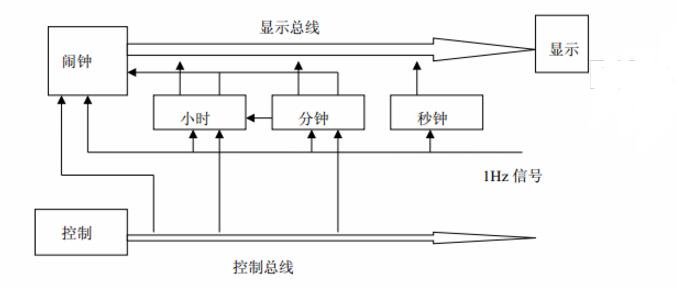

简单数字钟仿真电路图(二)

时钟信号分别加到各个模块,各个模块功能相对独立,框图如下:

该方案用总线结构,主要功能集中在模块内部,模块功能较为独立,模块间连线简单,易于扩展,本次设计采用此方案。

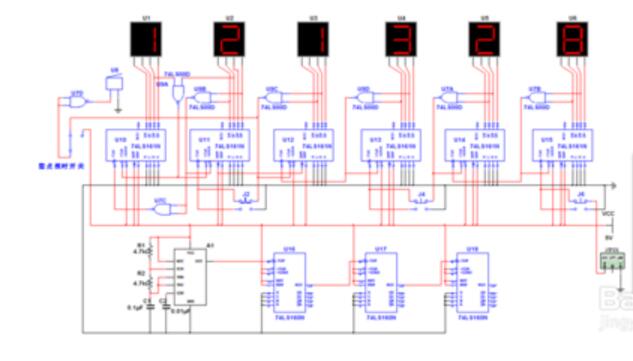

简单数字钟仿真电路图(三)

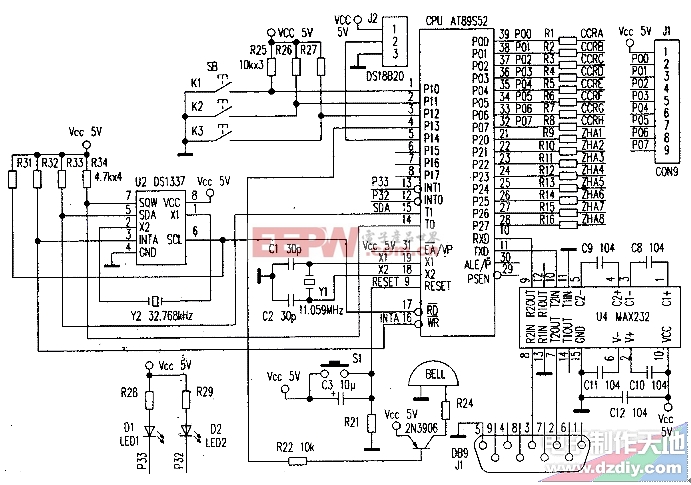

显示数码管能够正常跳动并进位,当整点报时开关打开时,在达到整点是蜂鸣器响;当按下校时开关时,数码管会跳动加“1”。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码