基于高速串行接口的雷达信号采集回放系统

编者按:针对雷达现场中复杂多变的电磁信号难以及时分析处理,本文提出了一种基于高速串行接口的雷达中频信号采集回放系统。该系统充分利用JESD204B高速串行接口和吉比特收发器,通过Xilinx Virtex FPGA芯片对其进行控制,实现雷达中频信号的高速、高精度、可靠、稳定采集和回放,有效地解决了高速数据流并行传输时存在码间串扰的问题。

回放过程类似于采集过程,不同的是数据进行拼接合路后被送入虚拟FIFO。该虚拟FIFO的主要作用是缓存定量数据以确保回放的信号完整连续,其主要由DDR3和FIFO构成,可实现多种位宽和多种速率的数据缓存[11]。如图4所示。上行FIFO和下行FIFO主要负责数据位宽和时钟速率的转换,FIFO控制器负责DDR3控制器核以及其它两个FIFO的读写控制。具体框图如图4所示。

4 实验结果与分析

为了验证系统传输的可靠性,我们配置ADS42JB69为递增码测试模式,并将采集部分后端的GTX与回放部分前端的GTX相连,完成整个系统的验证。结果如图5所示。

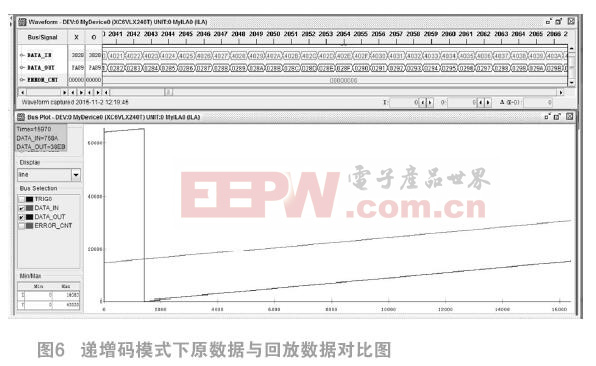

图5所示为采集信号做信道化后发送至GTX的数据图,其中TRIG1为ADC发送的递增码,TRIG2为信道化后送至GTX的数据。两路数据拼起来刚好就是一路完整的递增码。图6所示为发送数据和回放数据的对比图,图中ERROR_CNT为0表明信道化过程误码率为0,DATA_OUT是DTAT_IN延迟一段时间后的结果,实现了高速数据流稳定可靠传输。

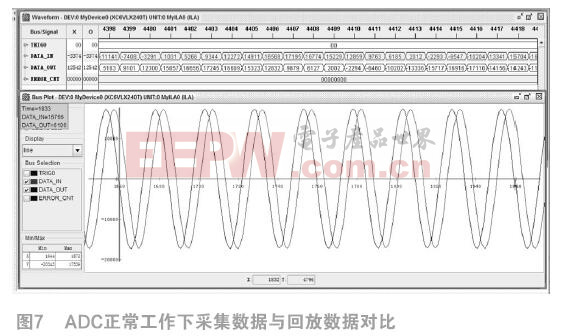

设置ADS42JB69为正常工作模式,输入信号频率为10MHz的单载频信号,输入和输出对比结果如图7所示。从图中可以看出,误码率为0,输出结果也很理想。

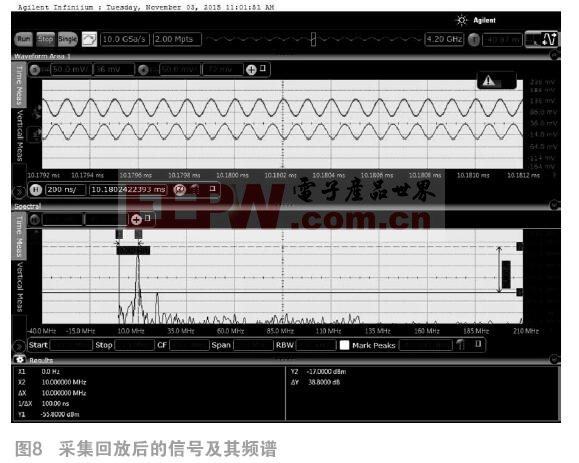

图8 所示为采集的数字信号进行回放所得信号及其频谱,上方信号为ADC采集的信号,下方信号为经过信道化后回放的信号。从频谱图可以看出信号频率在10MHz,主瓣与旁瓣相差38.8dB,达到项目的性能要求。整个系统高效快速地实现了雷达中频信号的采集以及回放。

5 结束语

随着雷达工作环境越来越复杂,对现场电磁信号的采集与重现工作也变得越来越重要。面对并行传输高速数据流方式误码率居高不下的瓶颈,本文提出了一种基于高速串行接口的雷达中频信号采集回放系统并上板得以验证。该系统利用JESD204B接口与GTX接口的兼容性,完成了双通道模拟信号高速高精度采集/回放以及稳定可靠传输,不仅使得高速数据流的传输成为可能,而且催生了采样速率更高的模数转换器。系统设计简单、数据处理方式灵活和通用性强,对高频雷达信号采集和高速采集数据传输有积极的影响。

参考文献:

[1]田耕,胡彬,徐文波.Xilinx ISE Design suite 10.x FPGA开发指南[M].北京:人民邮电出版社,2008.

[2]JonathanHarris.JESD204标准解析[J].今日电子: 2012,(12):31-33.

[3]JEDEC. Serial Interface for Data Converters[S].USA:JEDEC,2012:1 -145.

[4]Xilinx. Virtex-6 Family Overview[EB].USA:Xilinx,2009.

[5]李坤,朱红.virtex-6 GTX高速串行传输原理与仿真[J].大众科技:2010.

[6]Xilinx. Virtex-6 FPGA GTX Transceivers User Guide [EB]. USA:Xilinx,2009.

[7]TI. ads42jb69 [Z].USA:TI,2012.

[8]Analog.AD9142 [Z].USA:Analg,2012.

[9]Xilinx.FIFO Generator v4.4 User Guide[EB].USA:Xilinx,2008.

[10]席鹏飞,范晓星,冉焱,等.基于RocketIO的FPGA互连研究及应用[J].电子科技,2015.

[11]徐文波. Xilinx FPGA开发实用教程[M].第2版.北京:清华大学出版社,2012.

本文来源于中国科技期刊必威娱乐平台 2016年第5期第73页,欢迎您写论文时引用,并注明出处。

关键词: 高速串行接口 采集回放 Xilinx Virtex-6 201606

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码