TMS320C6678存储器访问性能 (下)

从上面的测试结果可以看出,多核同时访问相同DDR bank 中不同页的性能比多核同时访问不同DDR bank 中不同页的性能差很多,原因就是页切换的额外开销。

从上面的测试结果还可以看出,DDR 的带宽 (1333 x 8 = 10666MB/s)对所有DSP 核同时访问来说是不够的,DSP 核的优先级对它获得的带宽有明显影响。当优先级相同时,带宽在多个核之间平均分配;而当优先级不同时(上表中第二列是每个主模块的优先级),优先级低的核得到的带宽比较小。

为了防止低优先级的主模块被“饿死”,DDR 控制器提供了老请求优先级临时提高的功能。我们可以通过配置一个计数器,当一个老的请求的等待时间超过这个计数值时,它的优先级会被临时提高。如果没有特殊说明,本文所有测试中这个计数周期都被配置成4x16=64 个DDR3CLKOUT 时钟周期。在64 个DDR3CLKOUT 时钟周期内,可以传输64x2x8=1024 bytes。

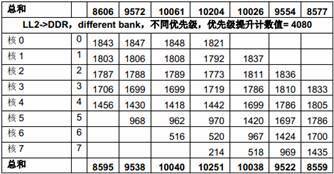

表11 是在1GHz C6678 EVM(64-bit 1333MTS DDR)上用不同的优先级提升计数值测得的数据。表中第二列是每个主模块的预设优先级。

表11 DDR 优先级提升计数值的影响

从上面的测试结果可以看出,优先级提升计数值=0 实际上使得预设的优先级不起作用。当这个计数值越大是,预设的优先级起的作用越大。所以,在实际应用中,设计者需要根据应用的需求来选择一个合适的值。

2.2.2 多个EDMA 共享DDR 的性能

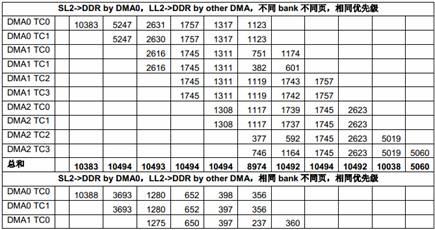

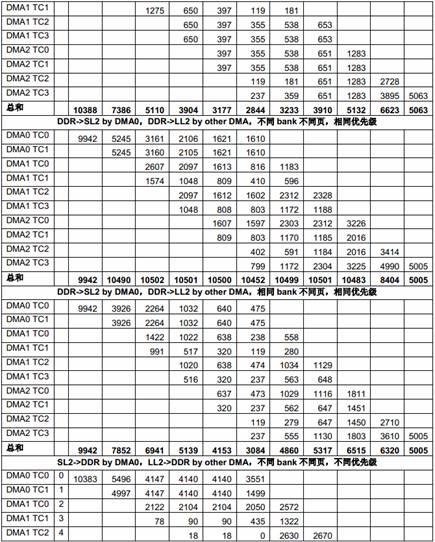

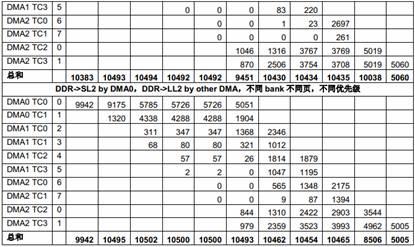

下面的表格列出了不同场景下多个EDMA TC 共享1GHz C6678 EVM 上64-bit 1333MTS DDR 的性能。

表12 多个EDMA 共享DDR 的性能

由于总共有10 个EDMA TC,而只有8 个DSP 核,在这些测试里,8 个TC 在DDR 和8 个核的LL2 之间传输数据,另两个TC 则在DDR 和SL2 之间传输数据。

从上面的测试结果可以看出,DDR 的带宽 (1333 x 8 = 10666MB/s)对所有EDMA 同时访问来说是不够的,EDMA TC 的优先级对它获得的带宽有明显影响。优先级低的EDMA 传输得到的带宽比较小。对负载很高的情况下,一些低优先级的传输可能会被“饿死”,也就是说,得到的带宽为0。

根据Table 6中列出的不同EDMA TC 的区别,EDMACC1 TC1 和TC3,EDMACC2 TC1 和TC2在某些情况下获得的带宽会比其它TC 小,即使优先级相同。

从上面的测试结果还可以看出,多个DMA 同时访问相同DDR bank 中不同页的性能比多个DMA同时访问不同DDR bank 中不同页的性能差很多,原因就是页切换的额外开销。当DDR 负载加重时结果变得更差。最坏的情况下,页切换的额外开销会占用整体传输时间的绝大部分,从而使总吞吐量急剧下降。

页切换的概率,也就是,多个主模块访问相同DDR bank 的概率取决于同时访问的主模块的个数和DDR bank 个数。例如,4 个DMA 随机访问8 个bank 的DDR 存储器,至少两个TC 访问相同的bank 的概率是:

表13 列出了理论上,多个主模块访问相同bank 的概率:

表13 多个主模块访问相同bank 的概率

为了减少DDR 页切换次数,如果有多个传输,有的要访问已经打开的页,有的要访问没有打开的页,C6678 的DDR 控制器一般情况下会让对已经打开的页的访问先执行。

3. 总结

总的来说,DSP 核可以高效地访问内部存储器,而用DSP 核访问外部数据则不是有效利用资源的方式;IDMA 非常适用于DSP 核本地存储器(L1D,L1P,LL2)内连续数据块的传输,但它不能访问共享存储器(SL2, DDR);而外部存储器的访问则应尽量使用EDMA。 为了充分利用cache,DSP 核应尽量连续访问。

EDMA 的ACNT 越大,效率越高。

SL2 有足够的带宽来支持所有核的同时访问。DDR 的带宽对所有核同时访问来说是不够的,DSP核的优先级对它获得的带宽有明显影响。

DDR 性能受页切换的影响很大,为了减少DDR 页切换应该尽量每次访问大块数据。

关键词: TMS320C6678 存储器

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码