TMS320C6678存储器访问性能 (下)

由于总共有10 个EDMA TC,而只有8 个DSP 核,在这些测试里,8 个TC 在SL2 和8 个核的LL2 之间传输数据,另两个TC 则在SL2 和DDR 之间传输数据。

尽管SL2 本身的带宽非常高,但所有EDMA 访问SL2 时都需要经过内部总线交换网络的一个相同的端口,这个端口就成了这种情况下的瓶颈。这个端口的理论带宽是500MHz x 32 bytes = 16000MB/s。如果所有EDMA 传输的优先级相同,带宽会在这些传输之间平均分配。而当优先级不同时(上表中第二列是每个主模块的优先级),优先级低的EDMA 传输得到的带宽比较小。对负载很高的情况下,一些低优先级的传输可能会被“饿死”,也就是说,得到的带宽为0。

根据Table 6中列出的不同EDMA TC 的区别,EDMACC1 TC1 和TC3,EDMACC2 TC1 和TC2在某些情况下获得的带宽会比其它TC 小,即使优先级相同。

2.2 多个主模块共享DDR 的性能

多个主模块同时访问DDR 时,DDR 控制器会根据主模块的优先级进行仲裁。

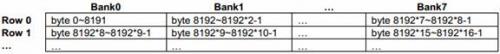

C6678 的DDR 控制器支持包含1,2,4,或8 个banks 的DDR 存储器。现在大多数DDR3 存储器都包含8 个bank,以C6678 EVM 上的DDR 存储器为例,它的组织结构如图11 所示。请注意,对不同的DDR 存储器,每一行的大小可能会不同。

图11 DDR bank 数据组织结构

尽管DDR 存储器有多个bank,但与SL2 的bank 不同的是,它们并没有独立的总线与控制器相连,而是共享相同的总线接口。所以,DDR 存储器bank 的个数并不直接的影响带宽,但它却显著的影响多个主模块共享DDR 的效率。

DDR SDRAM 的访问以行或页为基础。一个主模块在访问某个页中的数据之前,这一页必须首先被“打开”,然后这一页中的内容才可以被随意访问。如果主模块想访问同一个bank 中另一页中的数据,必须先关闭原先的页,然后打开新的一页。而页切换(关闭/打开)操作需要消耗额外的时钟周期。

每个bank 只可以有一页被打开,DDR 存储器的bank 数越多,页切换的概率就越小。例如,一个主模块在访问了bank0 的0 页后,它可以访问bank1 的1 页而不用关闭之前访问的bank0 的0页,然后这个主模块可以自由的在这两页之间访问而不会产生页切换。包含8 个bank 的DDR 存储器可以有8 页同时被打开。

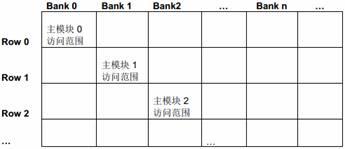

为了测试页切换的影响,我们定义了两种测试的数据结构。

图12 多个主模块访问相同DDR bank 的不同页

上面的情况是最坏的情况,页切换的额外开销被最大化。每换一个主模块访问就会导致一次页切换。

下面的情况则是最佳情况,每个主模块始终访问打开的页,而不会有任何页切换发生。

图13 多个主模块访问不同DDR bank 的不同页

2.2.1 多个DSP 核共享DDR 的性能

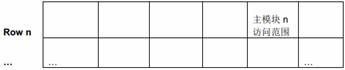

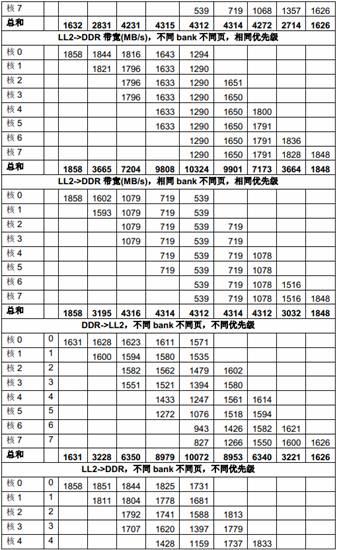

下面的表格列出了不同场景下多个DSP 核共享1GHz C6678 EVM 上64-bit 1333MTS DDR 的性能。每个主模块反复访问自己在DDR 中的数据buffer,在相同的时间内(大概2 秒),每个主模块传输的数据量被统计;而每个主模块获得的带宽则由数据量除以时间计算出来。

在这些测试中,DDR 是cacheable 且prefetchable 的,L1D cache 是32KB,L2 cache 是256KB,prefetch buffer 被使能。我们没有测试Non-cacheable 的情况是因为Non-cacheable 情况下每个核需要的带宽比cacheable 的情况下要少很多。

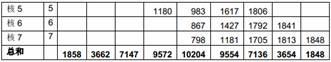

在下面的表中,每列是一个测试场景的结果,不同测试场景的主要区别是同时访问存储器的主模块的个数,格子中的数据代表相应的主模块在这个测试场景下获得的带宽,一列中的空格代表对应的主模块在这个测试场景下未被使用。最后一行中的数据是在这个测试场景下所有主模块获得的带宽的总和。

表10 多个DSP 核共享DDR 的性能

关键词: TMS320C6678 存储器

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码