采用PLL技术的接收机射频前端的设计

3.3、解调

接收机解调部分采用AD 公司的解调芯片,该芯片工作频率从50MHz 到1000MHz,包括正交下变频器,内置可控增益放大器和偏置电路。其内置VGA,控制电压由外部提供并可调增益大小,增益可调范围为44dB。

输入芯片的中频信号为了满足芯片的输入功率要求,加入了功率驱动放大链路,经放大后输入解调芯片的功率约为-40dBm 左右。因为解调芯片对第二本振信号内置了二分频器,所以第二本振信号频率应该是所需频率的两倍。

输出的I/Q 两路信号分别再经过运放电路进行放大,最终输出给数字基带部分进行处理。

4、实际测试结果

实际测时,输入信号频率为831MHz,通过在单片机编写控制字程序设置第一本振和第二本振的输出频率,第一次混频后得到的中频信号频率为140MHz,第二次混频后解调输出频率为1MHz 的I/Q 两路信号。本振的输出信号如下图所示:

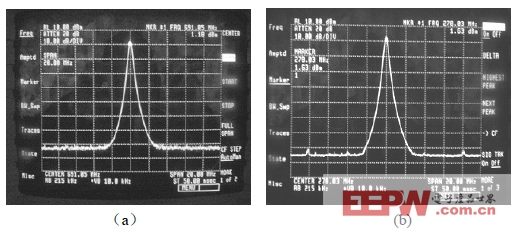

图6、(a)第一本振输出(b)第二本振输出

可以看到锁相环完成频率锁定,第一本振锁定在691MHz,因为解调芯片对第二本振信号内置了二分频器,故第二本振设计锁定在278MHz。从图中可知输 出信号杂散均小于-70dBc,锁相芯片在它要求的频率上工作正常,设计的结果也符合了系统对PLL 本振电路的要求。在锁相环输出信号之后,加入一个衰减网络,使输入到混频器和解调芯片的本振信号功率满足器件输入功率要求。

接着对整机进行测试,结果如下:

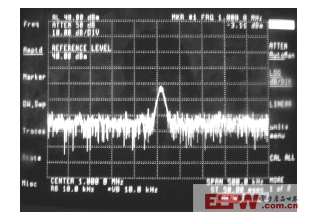

图7、实际解调输出信号

解调输出后得到信号频率为1MHz 的基带信号。固定AGC 增益值的情况下,即此时衰减值固定为0dBm,改变输入射频信号的功率,每增加10dBm,输出I/Q 信号功率增加约为10dBm,整机线性度[10]良好,注意此时应该在较低功率范围内调节输入功率,保证输出I/Q信号功率不会过大。经测试,接收机的最小可接收检测信号功率约-118dBm。

在 接收机中,解调输出I/Q 两路平衡是非常重要的指标。由于接收机信道特性不同,本振信号相位误差等诸多的因素都会导致I/Q 两路基带信号增益不平衡。若I/Q 失配,则会导致I/Q 误码率增高,严重影响解调性能。在本设计中,在选取芯片、设计电路中充分考虑到此问题,实际I/Q 两路输出基本做到了平衡输出。

5、结论

本文研究了使用PLL 的接收机原理和实现方案,并成功的用软硬件平台对其实现。本文的创新点在于成功的运用两个锁相环电路实现第一、二本振信号,试验结果表明锁相环有锁定时间短,相位噪声小,性能稳定等优点。实测结果表明接收机性能良好,指标达到了系统设计要求。

现代射频接收机主要是向高线性、大动态范围,高灵敏度,高分辨率等方面发展。如何采取有效的方法来提高接收机的抗干扰能力,降低超外差式接收机的成本,使得整体性能得以改进,是当今研究的热点方向,对接收机的研究有着非常重要的意义。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码