基于VHDL的QPSK调制解调系统设计与仿真

摘要:文中详细介绍了QPSK技术的工作原理和QPSK调制、解调的系统设计方案,并通过VHDL语言编写调制解调程序和QuaitusII软件建模对程序进行仿真,通过引脚锁定,下载程序到FPGA芯片EP1K30TC144-3中验证。软件仿真和硬件验证结果表明了该设计的正确性和可行性,由于采用FPGA芯片,减小了硬件设计的复杂性,该设计具有便于移植维护和升级的特点。

关键词:VHDL;QPSK;FPGA;QuartusII

QPSK调制技术在数字通信调制技术中占有非常重要的地位,将通信技术与FPGA结合是现代通信技术发展的一个必然趋势。QPSK技术具有抗干扰性能强、误码性能好、频谱利用率高等优点,目前广泛应用于数字通信、数字视频广播、数字卫星广播等领域。文中详细介绍了QPSK技术的工作原理,完成QPSK调制、解调的系统设计方案,并通过VHDL语言编写调制解调程序,通过QuartusⅡ软件对模块和程序进行仿真,并通过引脚锁定,下载到FPGA芯片EP1K30TC144-3中,软件仿真和硬件验证结果表明了该设计的正确性和可行性。

1 基于FPGA的QPSK调制解调系统设计

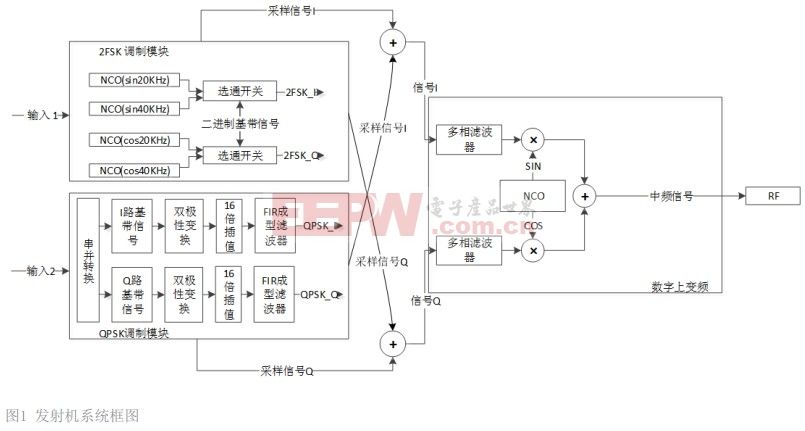

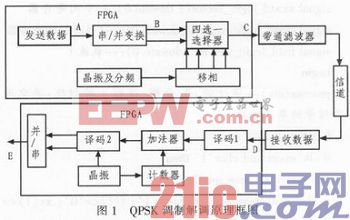

四进制绝对移相键控(QPSK或4PSK)利用载波的四种不同相位来表示数字信息。由于每一种载波相位代表两个比特信息,因此每个四进制码元可用两个二进制码元的组合来表示(常被称为双比特码元),一般用格雷码排列。调制解调的实现原理框图如图1所示。由图1可知,电路主要由分频器和四选一开关等组成,分频器对外部时钟信号进行分频和计数,并输出4路频率相同而相位不同的相干数字载波信号;晶振及分频、移相电路分别送出调相所需的4种不同相位的载波,按照串/并变换器输出双比特码元的不同,逻辑选相电路输出相应相位的载波。四选一开关是在基带信号的控制下,对4路载波信号进行选通,输出数字QPSK信号。但这还不是真正的QPSK信号,需要在FPGA器件外部加一个D/

A变换器,将输出转换为模拟信号。

由于QPSK信号可以看作两个载波正交2PSK信号的合成。对QPSK信号的解调可以采用与2PSK信号类似的解调方法进行解调,一般情况下采用相干解调,得到较好的解调效果。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码