基于FPGA和虚拟仪器的DDS信号发生器设计

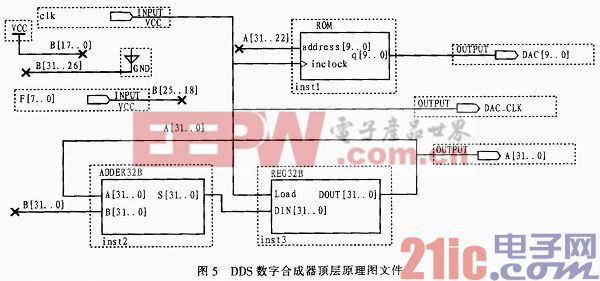

直接数字合成器由3部分组成,如图5所示。

其中:

1)ADDER32B作为32位数据加法器,提供可控步进的频率值;

2)REG32B作为32位移位寄存器,与ADDER32B一起组成累加器,将接收到的32位数据反馈到ADDER32B完成以外部端口F为键控频率字(即上文提到的)的步进;

3)ROM作为读取存储器波形数据,根据步进地址读取存储器中的10位长度的波形数据,送入DA转换器。

3 DDS信号发生器结果分析

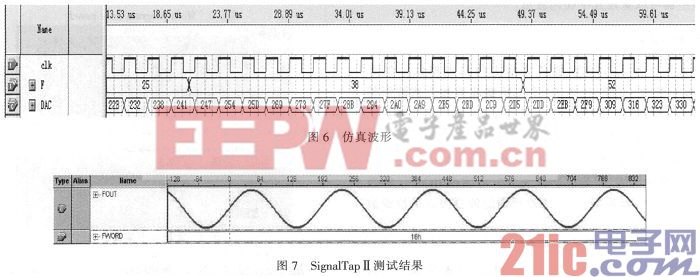

图6为仿真波形,可以看到,对于不同的频率控制字F给出的不同值,对应每一个时钟输出的采样点的步幅变化不同。图7为采用Quartus Ⅱ自带的测试工具SignalTapⅡ(嵌入式逻辑分析仪)对设计结果进行分析,如图7所示为F键控频率字设为16H时生成的正弦信号。图8是在示波器上观察的由DAC产生经低通滤波器处理后的真实波形。

4 结束语

文中采用LabVIEW虚拟仪器技术结合FPGA技术实现的DDS信号发生器,通过利用计算机的强大功能,把传统仪器的设计、编辑都放到计算机上完成,并通过通讯接口传输数据,实现不同波形的输出。通过对系统仿真和实际测试,结果表明该DDS信号发生器不仅能产生理想的输出信号,还具有集成度高。稳定性好和扩展性强等优点。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码