基于FPGA和虚拟仪器的DDS信号发生器设计

摘要:将虚拟仪器技术同FPGA技术结合,设计了一个频率可控的DDS任意波形信号发生器。在阐述直接数字频率合成技术的工作原理、电路构成的基础上,分别介绍了上位机虚拟仪器监控面板的功能和结构,以及实现DDS功能的下位机FPGA器件各模块化电路的作用。经过设计和电路测试,输出波形达到了技术要求,工作稳定可靠。

关键词:DDS;FPGA;LabVIEW;信号发生器

信号发生器是一种常用的信号源,广泛应用于通信、测量、科研等现代电子技术领域。信号发生器的核心技术是频率合成技术,主要方法有:直接模拟频率合成、锁相环频率合成(PLL)、直接数字合成技术(DDS)。DDS是开环系统,无反馈环节,输出响应速度快,频率稳定度高。因此直接数字频率合成技术是目前频率合成的主要技术之一。文中的主要内容是采用FPGA结合虚拟仪器技术,进行DDS信号发生器的开发。

1 DDS工作原理

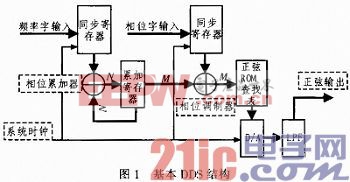

图1是DDS基本结构框图。以正弦波信号发生器为例,利用DDS技术可以根据要求产生不同频率的正弦波。

DDS电路主要由相位累加器、相位调制器、正弦ROM查找表、DAC和低通滤波器构成。其中,相位累加器是整个DDS的核心,完成相位累加的功能。下面对相位累加器的输入即相位增量进行分析。

对于正弦信号发生器,它的输出可以用下式来描述:

Sout=Asinωt=Asin(2πfoutt) (1)

其中Sout是指该信号发生器的输出信号波形,fout指输出信号对应的频率。正弦信号的相位:θ=2πfoutt。在一个clk周期Tclk,相位θ的变化量为:

![]()

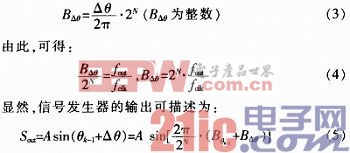

为了用数字化逻辑实现电路,必须对△θ进行数字量化,把2π切割成2N份,由此每个clk周期的相位增量△θ用量化值B△θ来表述:

其中θk-1指前一个clk周期的相位值。

由上面的推导可以看出,只要对相位的量化值进行简单的累加运算,就可以得到正弦信号的当前相位值,而用于累加的相位增量量化值B△θ(也叫频率控制字)决定了信号的输出频率fout,并呈现简单的线性关系。直接数字合成器DDS就是根据上述原理而设计的数字控制频率合成器。

从本质上看,DDS是一个恒定高频率运行的多位计数器。在溢出时,通过利用一个多位控制字来设置计数器步进的尺寸,允许计数器过零。计数器的高阶位用来寻址存储设备,该设备保持生成的一个波形周期的数字记录。高频时钟每前进一单位,计数器便步进一次,存储器也将生成一个新的地址字,而新的波形数据值将会发送到DAC。DDS主要有3个优点:1)输出信号的频率精度可以达到作为发生器参考信号使用的晶体控制振荡器的水平;2)DDS发生器可以生成非常高的频率精度;3)如果有RAM波形存储器,那么DDS函数发生器可以重现几乎任何波形。

2 系统设计

该系统采用LabVIEW软件完成上位机虚拟仪器的开发,生成正弦波、方波、三角波、手工绘制波形和公式波形等波形数据,实时显示于前面板并通过VISA串口将波形数据传送至FPGA存储器。下位机采用Alter公司的FPGA芯片EP1C3T144C8开发,通过VHDL语言软件式的硬件设计方法完成DDS模块开发,根据频率控制字数值读取ROM中的波形数据送入D/A转换器,最后通过低通滤波器完成平滑滤波输出。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码