以较高的开关频率在负载点 (POL) 应用中工作

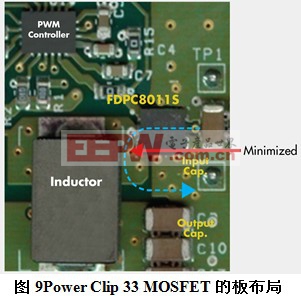

这一小尺寸、高效率的高频封装使得总体电源设计具有非常小的占位面积。 MOSFET、输入电容、电感和输出电容都嵌入到一个非常小的区域。 小尺寸电源系统最小化了开关节点区域,降低了从 SW 节点辐射出电磁干扰 (EMI) 噪音的风险。

封装底部的裸露 GND 和 V+ 焊盘支持从 MOSFET 晶圆到铜箔到环境的高效热耗散路径。

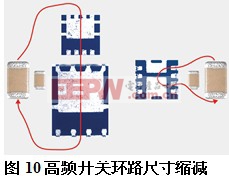

在设计具有最少寄生参数和最佳开关性能的封装时,输入电容与封装 V+ 到 GND 引脚之间形成的小环路大小至关重要。 Power Clip 封装上优化的 V+ 和 GND 引脚布局支持输入电容非常紧密的布局,以最大限度地减少环路面积,并减少寄生电感和开关损耗。

如图10所示,在 Power Clip 设计中,高频开关环路显著减小。 在开关转换期间,比如从 LS-off到 HS-on或从 HS-off到 LS-on,电流必须快速从一个 MOSFET 转换到另一个。 这一转换操作发生在由两个功率 MOSFET 和输入电容组成的环路之间。 该环路中的瞬态开关比输出电感中电流的纹波频率快几个数量级。 因此,这是决定开关损耗的环路。 对于一对分立式 MOSFET ,开关电流在返回到输入电容之前必须流经整个 HS 和 LS Mosfet。 对于 Power Clip 封装,电流出入于一个紧密环路中封装的同一面,仅由两个引脚的间隔隔开。 在分立元件的布局中,高频环路大小受到 MOSFET 的封装尺寸的限制。 对于 Power Clip,环路大小受到输入电容的大小的限制。

为高频同步整流低压转化器优化设计的Power Clip 33 MOSFET

本节展示一个典型的电源系统的详细分步设计,并展示因高操作频率和高效率相结合而减小的板面积。

对于芯片组电源,选作目标工作条件的一个常见设计是 12 Vin,1.6 Vout和 25 Aout。 对于操作频率,选择了两个点: 300 kHz 和 600 kHz。 输入电容、输出电容和输出电感的元件尺寸都因较高的操作频率而减小。

较高的操作频率可改善瞬态响应,同时保持纹波不变,并减小电感和电容的元件大小。

表1展示操作频率为 300 kHz 和 600 kHz 时的设计示例。 与 300 kHz 的分立式 MOSFET 设计相比,在 600 kHz 时使用 Power Clip 33 MOSFET 可让设计人员节省 42% 的总 BOM 面积。

数据测量效率、功率损耗、温度上升

在一个同步降压转换系统中,MOSFET 的额定电流基于若干因数的折衷:

a. MOSFET 的最大 TJ

b. 输出功率

c. 效率

d. RΘJA 热阻

通过封装结构的显著改进以及高级硅技术,Power Clip 33 MOSFET 封装可在一个 3.3 x 3.3 mm 的占位面积中提供 20 A 解决方案。 为了评测 Power Clip 33 Dual MOSFET 的性能,我们测试了FDPC8011S和两个备用的大尺寸设计,即一对分立式Mosfet HS Power 33 (FDMC8588) / LS Power 56 (FDMS8560S) 和 FDMS3624 Power 56 Dual MOSFET。图11展示了封装尺寸的发展。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码