以较高的开关频率在负载点 (POL) 应用中工作

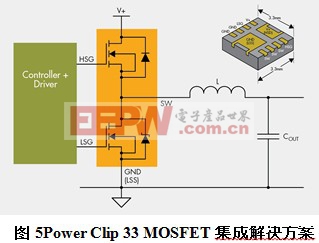

本文通过 Power Clip 33 MOSFET 展示了小尺寸元件解决方案的高频性能(参见图5),以及与传统分立式 Power 56 封装相比带来的效率提升。

Power Clip 33 MOSFET 封装

Power Clip 33 MOSFET 拥有卓越的高频开关操作性能。 关键设计特性是:先进的低 FOM 硅技术,结合一个散热优化的低电感铜夹互连封装。 它拥有最少的占位面积,使其更易于布线设计。

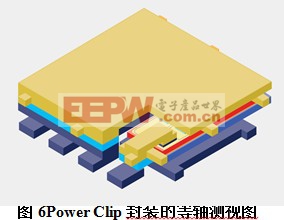

图6展示了封装结构的关键元素。 在这个双晶圆封装中,高侧 (HS) MOSFET 漏极朝下。 低侧 (LS) MOSFET 源极朝下。 从 HS 源极到 LS 漏极的互连通过一个大型铜夹完成。

如图7所示,相对于传统封装设计,比如分立式 Power 33、Power 56 或 Power Stage 56 Dual,寄生电阻和电感实现了大幅性能提升。

最大限度地减少电源路径寄生参数 – 要让一个同步降压电源拥有最优开关速度,必须最大限度地减少高频 (HF) 开关路径中的封装寄生电感;V+ 到 SW 到 GND (图5);并且必须最大限度地减少 V+ / GND 输入电容与 MOSFET 封装引脚之间的物理距离。 Power Clip 设计通过使用一个漏极朝下 HS MOSFET、晶圆之间的铜片夹和源极朝下 LS MOSFET 来实现这一点。 这实现了最小阻抗开关路径,其中在高频电源开关路径中无封装接线。 电源路径中唯一的互连是一个低电感、低电阻的铜夹。

增强的热性能 - 结构还优化了热性能。 典型 PCB 设计上的两个铺铜区域是 V+ 和 GND。 HS 漏极朝下 和 LS 源极朝下的 Power Clip 设计支持封装脚位与这两个铺铜区域之间的大面积连接。 铜夹支持卓越的晶圆与晶圆之间的热耦合。 这个独立于 HS 与 LS 晶圆之外的功率分区使两个晶圆之间具有低 RΘJA 热阻抗。

先进的硅技术 - 在该设计中使用的 MOSFET 技术是屏蔽栅极 PowerTrench® 工艺。 HS 和 LS 都设计有低单位面积电阻或 RSP,(mΩ/单位面积),以及低栅极电荷或 QGD,硅。 两个 MOSFET 都是极低 FOM (QGD*RSP) 元件。

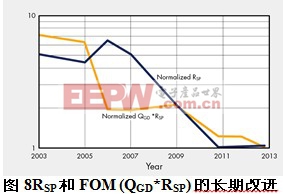

图8展示了飞兆归一化 RSP和归一化 FOM (QGD*RSP) 的长期改进。 飞兆在这两个参数上都实现了一致的大幅改进。 传导损耗直接与 RDS(ON)成正比,而开关损耗直接与 QGD相关。 对于一个给定 RDS(ON) MOSFET,随着其 FOM (QGD*RSP) 的减少,QGD 和开关损耗也随之减少。 飞兆的设计改进同时降低了两个损耗系数。

通过减少 RSP,飞兆能够为典型的电源系统设计较小的晶圆。 晶圆尺寸越小,栅极电荷 (QG) 和 QGD也就越小。 较小的晶圆尺寸也允许使用较小的封装,从而使封装寄生参数减少。 最终得到的是一个小尺寸低开关损耗的设计。

POL 转化器的布局优化 - 由于使用了最小的功率环路面积和印制板空间,Power Clip 33 MOSFET 封装有助于优化布局和提高系统效率。图9展示了一个 Power Clip 封装元件的布局示例。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码