基于GPS的恒温晶振频率校准系统的设计与实现

2 系统设计

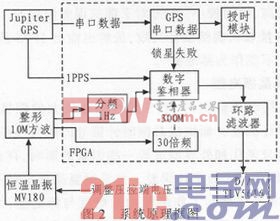

系统以FPGA作为控制器,芯片选用Altera公司的EP3C25E144C8,内部具有丰富的逻辑资源。开发平台是Quartus II集成开发环境,采用Vetilog HDL语言对各功能模块进行逻辑描述,并完成了逻辑编译、逻辑化简、综合及优化、逻辑布局布线,并使用Modelsim、Signalnap II进行逻辑仿真,实现系统的设计要求,系统的原理框图如图2所示。

2.1 数字锁相环

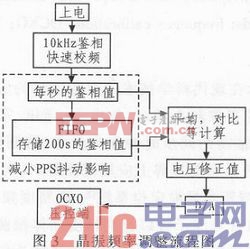

恒温晶振的频率调整功能是靠数字锁相环(DPLL)实现的,同模拟锁相环类似,它属于闭环的控制系统,由鉴相器(PD)、环路滤波器(LPF)、D/A转换器、压控恒温晶振(OCXO)组成。系统启动后,在FPGA内部,数字鉴相器模块首先以GPS接收机输出的10 kHz时钟信号作为基准源,对恒温晶振整形并经过分频后的10 kHz信号进行快速鉴相,用恒温晶振倍频后的300 MHz时钟对相位差进行量化,得到具体的超前或滞后数据,进而传递给环路滤波器模块,设置抖动门限参数,若相位超前或滞后量达到门限值,则迅速通过D/A转换器,对晶振的压控端电压进行相应调节。此方法可令晶振频率快速接近10 MHz,但是恒温晶振频率的改变需有一定的响应时间,快速调整压控端的电压会产生过调现象,频率稳定度不佳。

为进一步提高晶振频率的精度与稳定性,结合恒温晶振短期稳定度高的特点,在数字鉴相器模块中,以GPS的1PPS信号为基准,测量1PPS与恒温晶振分频出的1Hz信号的相位差。依据GPS没有累积误差的优点,在环路滤波器模块中采用滑动平均滤波法来降低GPS秒脉冲对测量带来的干扰,设计FIFO存储器来配合计算出最近200 s的平均相位差,通过不断对比短时的相位差及长时的平均相位差,分析相位差的长期与短期变化动态,实时调节恒温晶振的控制电压,保证晶振输出稳定且准确的10 MHz时钟信号。晶振频率调整的过程如图3所示,此方法简单实用,可有效抑制1PPS抖动对晶振造成的影响。

2.2 电路设计

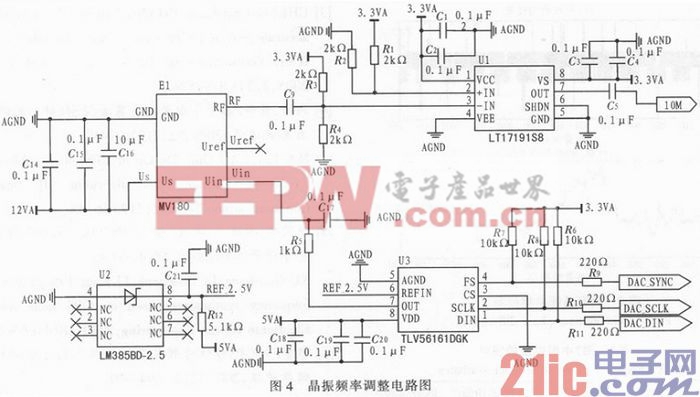

D/A芯片选用TI公司TLV5616,它是低功耗单片12位串行数模转换器,分辨率为4096,该芯片采用三线制(SCLK、SYNC、DIN)串行接口,SCLK方波信号为下降沿时,TLV5616读取DIN的电平信号,转化成相应的电压送往恒温晶振,用于晶振的微调,晶振频率调整硬件电路如图4所示。

2.3 授时功能

在许多现实的应用中需要毫秒、微秒、纳秒等这些更小的时间单位量,但是GPS接收机一般只能提供最小时间单位为秒的UTC时间,本系统在GPS基础上设计了授时功能。

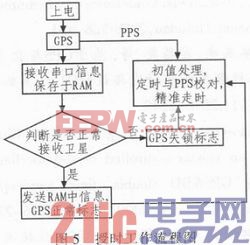

授时工作流程如图5所示,系统在FPGA中设计串口数据模块来接收GPs的SD01管脚发出的GPRMC格式数据,并将其存放在FPGA内部的双口RAM中,通过串口数据模块及数字鉴相器模块可以判断GPS接收机是否正常工作。若识别出准确的UTC时间和1PPS信号后,授时模块迅速从RAM中提取最新时间数据进行处理,得到初始时间值,当下一个1PPS上升沿到来后,系统在初值的基础上开始完全依靠高稳恒温晶振自行走时,并每隔5秒与准确的1PPS信号进行校对,如果发现本系统的时间与1PPS不同步,那么系统时间将会短暂停滞或快速跳进,达到与1PPS同步,保证时间信息输出的连续性与准确性;若GPS接收机非正常输出1PPS信号,则不进行校对,直到1PPS正常后再恢复校对功能。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码