基于FPGA的水声信号采样存储系统设计

3.1.2 主端口IP 核

因为SDRAM 主控IP 核在NiosII 软核CPU 总线控制下作为从端口,所以不能主动发起 读写操作,因此必须新建第二条AVALON 总线,设计读写主端口IP 核,才能实现读写外接 SDRAM 芯片的功能。主端口IP 核的时序操作,是对主控IP 核的时序转接,面向SDRAM 控制器进行控制。根据读写使能信号不同,进行不同时序传送。

3.2 软件程序设计

NiosII CPU 作为软核,可方便进行模块化操作,具有可移植,可配置,易整合的特点。 在本设计当中,软件设计主要实现以下五种主要功能:单点写SDRAM,单点读SDRAM, 数据飞读,连续写SDRAM,连续读SDRAM 的功能。在程序当中留有接口,方便其他功能 整合,符合模块化设计的要求。

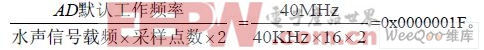

首先,完成功能的初始化,主要是设置选择操作模式与存储 AD 数据的时钟分频系数。 作为SDRAM 的读操作必须满足写满之后,方可进行,所以初始化主控IP 核为写SDRAM 操作。设置分频系数可以按照如下公式计算:

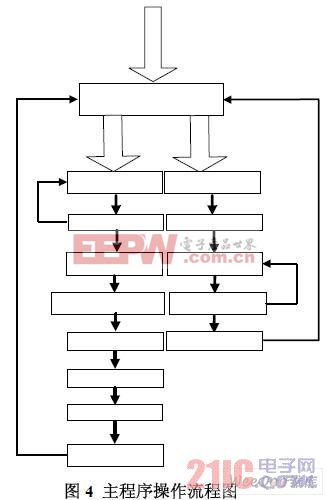

其次,通过对于串口进行协议解析,分别实现五部分预设功能。主程序操作流程如图4所示。

实现的五部分功能依次为:

(1) 单点写SDRAM 操作:CPU 给出地址,数据,以及写操作选择信号。

(2) 连续写SDRAM 操作:CPU 只是给出写操作选择信号,由主控IP 核将AD 数据写入至SDRAM 环形存储区域内。

(3) 数据飞读操作:只需要读取飞读数据寄存器,可以将当前状态AD 输入值送回至CPU,侦测当前状态。

(4) 单点读SDRAM 操作:CPU 送出读SDRAM 地址,然后选择读操作,设置控制寄存器为0x00000001,启动读操作。最后将读回数据通过串口实时回传。

(5) 连续读SDRAM 操作:是将基本读操作进行循环执行。设置串口回传缓冲区为80 字节,连续读SDRAM 数据并连续填写缓冲区,一旦填满,则启动串口发送。同时,读地址在每次读操作结束后自动加一,当操作次数达到环形空间最大存储数量时,停止连续读操作。

4 结束语

本设计作为水下无线传感器网络(UW-ASN)节点的设计组成部分,具有结构清楚,功 能完善,整合性强,性能可靠的特点。设计整体架构的模块化操作以及可编程性,使得整个 设计开发的具有灵活性与低风险性。经项目试验验证,该数据采集与存储设计满足传感器节 点的功能要求,为水声通信试验顺利进行以及水下无线传感器网络的功能完善提供可靠保证。

本文创新点:在系统功能设计当中,充分考虑了模块的可重用性和可移植性,通过IP核的设计实现底层驱动,提高系统集成度,充分发挥了SOPC技术的优势。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码