基于FPGA的水声信号采样存储系统设计

3 系统整体设计

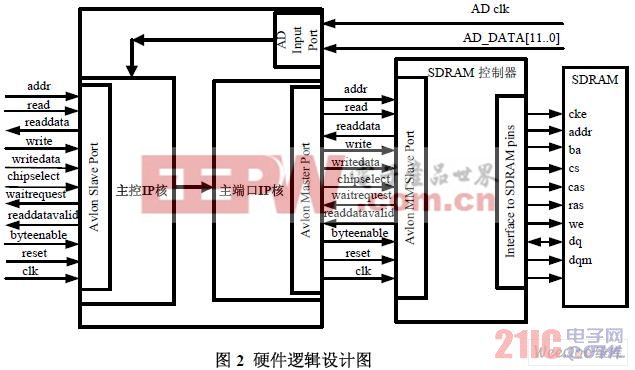

3.1 硬件逻辑设计

硬件逻辑设计主要包括主控IP 核设计与主端口IP 核设计两部分工作,分别实现对于 AD 采样数据的存储和读取时序控制,以及AVALON 总线的主端口建立的目的。硬件逻辑 利用IP 核模块化,移植性好的特点,方便整合到传感器节点的整体设计当中。作为传感器 节点的组成部分,为水声通信试验的顺利进行提供可靠保证。 硬件逻辑设计图,如图 2 所示。

3.1.1 SDRAM 主控IP 核设计

主控IP 核通过对于QuartusII 自带的SDRAM 控制器进行控制,实现变速率AD 采样的 功能,以及读写SDRAM 的逻辑功能。由于SDRAM 控制器实现了对于SDRAM 芯片的时 序操作,所以读写时序设计是针对SDRAM 控制器进行[3]。

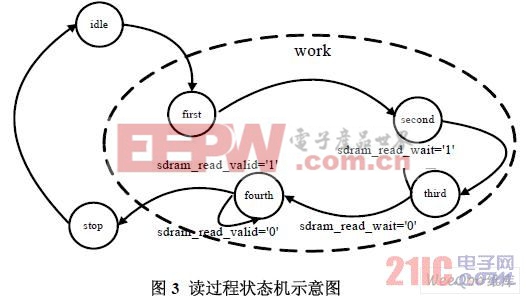

系统读 SDRAM 操作分为数据飞读与数据环形读取两种功能[4]。其中,数据飞读是将当前AD 采样值送回至CPU,并通过串口返回到前置机,方便实时数据监控。对于数据环形 读取SDRAM 操作,通过设置首地址指针寄存器,在每次写操作之后自动加一,实现环形 存储水声通信数据的目的。在每次环形数据读取操作发起之前,预读首地址指针寄存器,以 此为起始地址,始终读取最新时刻的采样存储数据。 读操作过程主要状态机,如图 3 所示。

其中 work 过程包含的独立状态机,由如下四部分构成:

(1)first:片选有效,读使能有效,送读SDRAM 地址。

(2)second:读使能有效,满足SDRAM 控制器读时序要求。

(3)third:判断sdram_read_wait 信号值,如果为1,则维持当前状态,同时读使能信号置位;如果为0,则进入下一状态。

(4)fourth:判断sdram_read_valid 信号值,如果为0,则维持当前状态;如果为1,将读回数据写入读SDRAM 数据寄存器,同时读使能信号复位。

变速率AD 采集与数据环形存储操作主要是由主控IP 核写SDRAM 的过程实现。为保 持采样时刻数据的稳定性,系统对AD 时钟进行分频,通过设置不同分频寄存器,实现变速 率采样的目的。数据环形存储SDRAM 操作是靠每次分频时钟SDRAM_WRITE_CLK 的上 升沿触发,基本时序过程与读过程状态机类似。系统从0 地址开始写操作,一旦写满预设存 储区域,则从下一写时刻开始,数据写入初始地址,以此类推,实现环形存储操作。同时, 读写操作不能进行同时进行,通过读写选择控制器的设置,分别按照不同状态进行操作。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码