三阶单环Delta-sigma调制器在ADC中的应用

2.3 Verilog语言行为级建模

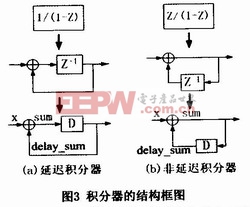

图2所示的是一种单路差异积分器调制器,可用延迟积分器和非延迟积分器,以及各种前馈和反馈路径组合而成。在Matlab结构中对应的积分器转换成Verilog硬件描述框图的过程如图3所示

本文使用Verilog硬件语言来实现单回路差异积分调制器,由时钟控制构成延迟积分器与非延迟积分器的相加动作。assign指令使等式两边永远处于活动状态,而alwavs指令将会在时钟正好触发时将sum的值存入寄存器delay_sum中,因此,所有的积分器将会在每一次时钟完成时完成一次累加动作。同理,非延迟积分器是由相同的程序代码组成。实现延迟积分器的程序部分代码如下表示:

3 模型的仿真结果

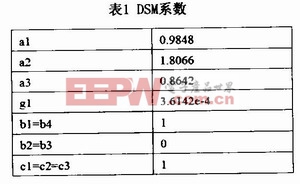

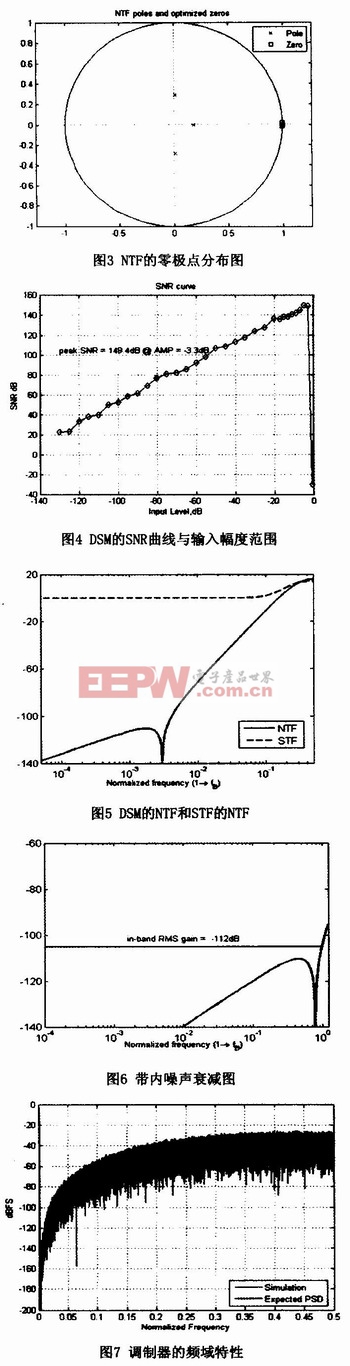

图3给出的是NTF的极点与零点图。很明显,NTF的零点均匀地分布在信号基带中,而不是集中在直流频率处。图4给出了输入幅度范围与SNR。图5给出了NTF和STF的幅频响应。可以看到,带内信号的衰减几乎是0,而图6显示噪声的衰减小于-110dB,满足带内噪声的要求。图7给出了调制器的频域特性图。图8给出的是在输入为42000,时钟频率为8.4MHz的verilog硬件描述语言的仿真结果,可以看出经过2μs后结果趋于稳定。

4 结论

本文提出一个用在ADC中的16位的3阶8级量化的三阶单环Delta-sigma调制器。为了提高电路性能,实现较高的SNR和DR,减少量化噪声的影响,在设计NTF时采用前馈方式和局部反馈的结构,并进行零点优化,通过这些方法优化了输出SNR,提高DR,降低量化噪声,使得电路对于量化噪声有较好的敏感度。根据仿真结果,这个DSM的峰值SNR可以达到145dB以上,在3阶的系统和128的过采样率下,达到相当高的SNR,之后用Verilog语言对调制器各电路模块进行建模与仿真。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码