5 Gsps高速数据采集系统的设计与实现

从图3(a)中的数据可以看出,各个通道均以约定的格式输出,说明ADC与FPGA之间数据接口已经准确连通。图3(b),输入正弦信号时用BUS PLOT工具将抓取到的数据实时画图,得到的波形平滑,计算其信噪比为42.9 dB,由式(2)计算得到ADC的有效位数为6.6 bit。实测表明,AD9520输出的2.5 GHz时钟以及EV8AQ160均具有较高的性能,整体指标达到设计要求。

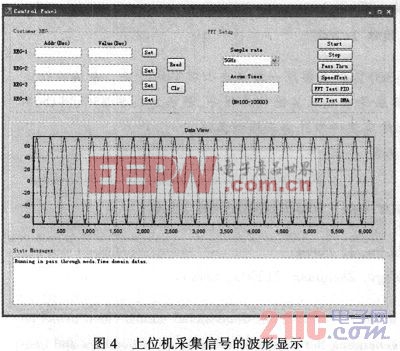

2)上位机数据结果显示

用户应用窗口程序的设计是在Visual Studio 2008环境下进行的,内部通过调用WinDriver提供的API函数及已编写的驱动函数,可以打开、查看、配置和关闭该PCI Express硬件设备。将系统配置为5 Gsps采样率的工作模式,用TeeChart画出实时采集到的波形,如图4所示,表明系统实现了数据的实时采集存储功能。

3 结束语

采用FPGA作为数据采集系统的控制核心,使用FPGA内部资源或者外部DDR3实现数据的缓冲存储,充分利用系统资源,便于调试和修改。实现了5 Gsps实时采样率、8 bits采样精度的高速实时数据采集系统。在完成电路的软件和硬件设计以后,通过对ADC和时钟进行测试以及上位机控制界面采集信号的波形显示,结果表明该系统可以稳定地工作,满足设计要求。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码