LVDS信号的PCB设计和仿真分析

2.1 PCB板叠层设计

使用Cadence16.3的SI工具进行信号完整性的仿真。

设计采用6层板的叠层结构,经过合理安排叠层厚度,通过Allegro计算,表面微带线宽6 mil线间距6 mil时,阻抗理论计算值分别为103和99.4 Ω。符合阻抗控制要求。内层没有走差分线,线宽设置为5 mil。

2.2 LVDS差分对的波形分析

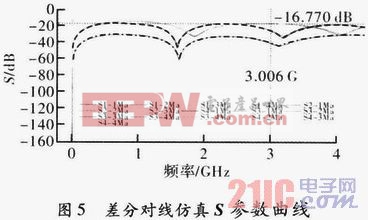

LVDS信号线之间的等距是为保证两者差分阻抗一致,减少反射。差分对的两条线之间要保持平行,防止耦合共模干扰。在叠层设置中,保持平行是为了保持阻抗连续,否则会产生延迟和抖动。通过S参数分析差分对阻抗(Differential Impedance)。从仿真如图3所示,S11在0~3.0 GHz的频域范围内,其最劣化的指标为:-16.770 dB以下,S22(虚线的曲线)也不劣于-17 dB。这说明该差分对的差分阻抗连续性很好。

通过Hspice的IN,OUT仿真,可以看出差分对良好的对称性。

3 结束语

LVDS在航天军工等方面具有广泛的应用,但是由于信号完整性的问题考虑不够,经常出现设计问题,文中从基于LVDS的高速信号下载器的约束设计进行论述,通过仿真研究,达到了设计目的。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码