高速互联链路中参考时钟的抖动分析与测量

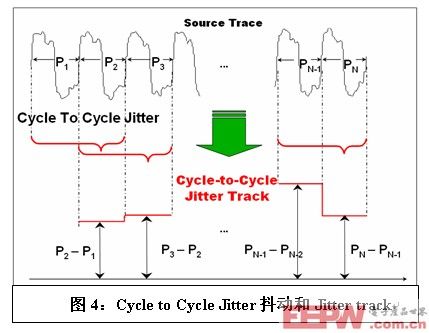

相邻周期抖动(Cycle to cycle jitter)是时钟相邻周期的周期差值进行统计与测量的结果。如图4所示,后一时钟周期减去前一时钟后作为统计的样本,C1=P2-P1, C2=P3-P2, Cn-1 = Pn - Pn-1,把C1到Cn-1进行数理统计,同理,可以计算出Cycle to cycle jitter的峰峰值和RMS值。

在上述三种常见的时钟抖动中,对于串行总线,通常是测量TIE抖动,比如高速收发器TX端的参考时钟。对于并行电路,通常是测量其时钟的周期抖动和相邻周期抖动,比如DDR SDRAM、PC主板上的FSB等等。

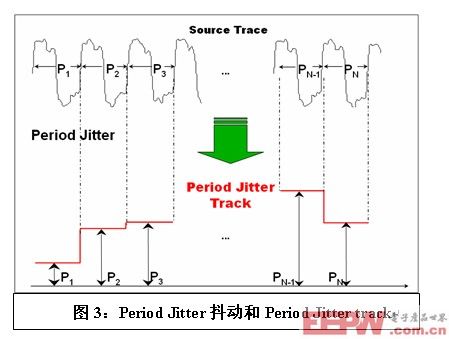

在图2、图3、图4中的红色曲线横轴是时间,纵轴是对应周期的抖动数值,该曲线反映了抖动随时间变化的趋势,称为抖动跟踪(Jitter track);将每个周期的抖动值(比如TIE抖动的I1、I2…In)作统计直方图,可以得到抖动直方图(Jitter Histogram);将抖动跟踪做快速傅立叶变换(FFT)计算可以得到抖动频谱(Jitter Spectrum)。

抖动跟踪是抖动在时域的表现形式,抖动频谱是抖动在频域的表现形式,抖动直方图是抖动在统计域的表现形式。各种测试仪器和分析软件对于抖动的测量和分析都是在这三个域中实现的。

如下图5为某100MHz时钟在时域、频域、统计域分析其TIE抖动的示意图。左上角的F2为某100MHz时钟,P1是时钟的TIE参数测量;右上角的F3是TIE抖动的直方图,直方图不是高斯分布,可见时钟存在固有抖动。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码