USB 2.0主控器软硬件协同仿真系统设计

2.2 本文设计的软硬协同仿真系统介绍

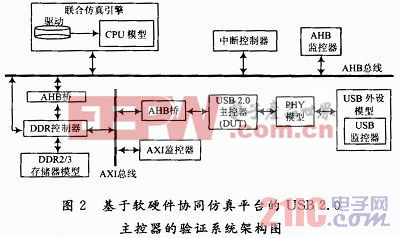

相对使用传统验证方法,本文设计的软硬件协同仿真系统使用抽象度较高的C语言编写测试激励,通过调用系统中CPU模型对外提供的API完成激励生成与响应检查。基于本引擎编写的测试激励可以方便的移植,所以在硬件仿真阶段就能调试SoC系统软件,不必等到FPGA平台设计完成或芯片设计完成后,从而大大节省了项目开发时间。图2是本文验证USB主控器功能的软硬件协同仿真的系统架构图。本验证环境由3大部分组成:联合仿真引擎,即CPU模型;总线架构及系统内存模块,包括一个DDR模型和DDR控制器;USB协议实现、检查模块,包括待验证的USB主控器、支持UTMI+接口的PHY、外设模型。在该平台下,联合仿真引擎(CPU模型)替换掉SoC中原有的CPU,是整个验证系统的核心也是整个系统设计的核心。通过使能信号触发联合仿真引擎工作来执行C程序,将软件对USB主控器的控制转化成总线时序,将软件和硬件交互的行为模拟到RTL侧。下文将对仿真平台中各个模块,重点对联合仿真引擎进行详细介绍。

2.2.1 基于TLM建模的联合仿真引擎及设计

使用软硬件协同仿真的方法验证USB主控器,只需要用C语言编写USB主控器驱动并将其集到成系统中进行仿真测试,因此要求CPU模型能够简单、高效地执行驱动程序,CPU在SoC中都是直接通过AHBMaster接口连接到总线(BUS)上,对SoC中要验证的IP来讲,CPU就是一个总线Mas ter,IP并不关心CPU是什么指令集,采用何种方式实现。基于此,本联合仿真引擎设计的CPU模型并没有采用基于特定指令集设计的复杂方法,而是采用基于SystemC事物级建模(TLM)技术构造了一个基于AHB协议的总线功能模型(BFM),实现了对CPU对SoC中其他模块所呈现的AHB Master接口的时序封装。这个BFM能和要验证的RTL模块进行连接和通信,它能够编译并解释基于C语言编写的驱动程序,并把这个驱动程序要执行的操作翻译成对应的AHB总线信号。通过层次化的封装,本联合仿真引擎把基于时钟时序精度的RTL的抽象层提升到没有任何时钟和时间概念的软件抽象层。同时,本引擎能取代任何CPU。不管SoC中真正使用的CPU是MIPS指令集、ARM指令集还是其他CPU,都能被本联合仿真引擎替代。

本引擎的CPU模型使用系统仿真用的工作站或者服务器的宿主CPU来运行验证工程师编写的基于C语言的测试激励程序,将需要的具体硬件行为通过Channel向下传送到RTL端。相对于直接使用SoC中CPU IP核的RTL的仿真,该引擎省去了CPU IP核取指令和运行指令的复杂的仿真、运算过程,大大节省了仿真运行的时间。本联合仿真引擎为软件人员和硬件验证人员分别提供了一些总线访问和中断处理的API,为了满足硬件验证的需要,另外设计了一些API可以实现让系统等待一定时钟周期或者时间、停止或重新开始仿真、不通过总线而可以快速访问系统存储器等功能。在系统中CPU模型对USB主控器和DDR控制器的配置均通过这2个模块对外提供的AHB Slave接口。

2.2.2 仿真系统的其他模块介绍

DDR2/3为系统内存,存储USB主控器正常工作需要的描述符和收发的数据。由于本系统中DDR2/3控制器只提供AXI Slave的数据接口,系统中CPU和USB主控器需要通过AHB桥将AHB从机的接口时序转换成AXI Master的接口时序,保证2个模块之间正常的数据通信。系统工作过程中AxI,AHB总线监控器监控2个总线活动,打印出报告信息,方便仿真结果检查。

USB主控器是待验证的主控器(DUT)。PHY模型提供UTMI+接口,有USB 2.0和USB 1.1两种接口分别支持EHCI接口和OHCI接口实现。外设模型包括一个PHY验证IP(VIP)和一个USB外设验证IP,模拟USB外设的行为。USB外设VIP中包含一个USB监控器模型,负责协议检查,记录事物传输进程,监控高速、全速和低速的USB传输,提供数据包级和事物级传输的监控,同时可以监控挂起、恢复和复位信号。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码