USB 2.0主控器软硬件协同仿真系统设计

摘要:为了能够充分、快速验证USB 2.0主控器的功能,设计了一个软硬件协同仿真平台。其中,CPU模型部分采用一种高效的SystemC模型,而不使用基于指令集的复杂CPU模型。测试用例采用抽象层次更高的C语言编写,通过调用仿真平台对外提供的API完成激励生成与响应检查。结果表明,该方式能够有效降低对仿真资源的占用,减少仿真时间;同时使软件人员能在IP的硬件验证阶段就能完成软件的设计测试工作,缩短软硬件接口整合时间,加快开发进度。

关键词:软硬协同;联合仿真引擎;CPU模型;通用串行总线;主控器;片上系统

USB由于具有传输速度快、支持即插即用和热插拔、供电方式灵活、总线结构简单、使用和扩展灵活等优点,已经成为业界主流的工业接口标准,并在SoC设计中得到了广泛的应用。在典型的应用案例中,USB主控器作为SoC中的一个子模块,和其他子模块有复杂的互联、通信关系,同时也受系统主CPU的控制。在这样一个复杂的系统中,如何验证USB主控器设计的正确性以及其和SoC系统其他模块协同工作的完整性对项目成功与否是非常关键的。本文设计了一种软硬件协同仿真平台来验证应用在数字电视SoC中的USB2.0主控器,本平台为SoC的验证提供了一个高效、系统的解决方案。结果表明效果良好。

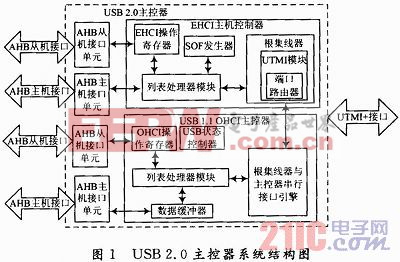

1 待验证USB 2.0主控器系统结构

本文验证的USB 2.0主控器完全兼容USB 1.1规范,EHCI主机控制器接口规范和OCHI主机控制器接口规范。该USB 2.0主控制器包含一个高速主控器和一个全速主控制器,其中高速主控器基于EHCI接口规范实现,用来和连接到根端口的高速(传输速率为480 Mb/s)模式外设进行通信。全速模式主控制器基于OHCI接口规范实现,使USB 2.0主控器可以与全速和低速(传输速率为12 Mb/s和1.5Mb/s)外设进行通信。系统CPU可以通过该主控器的AHB Slave接口对其进行控制。该主控器中还包含AHB Master接口单元,能够扮演AHB Master的角色直接控制主控器与系统存储器之间的数据交换,不需要通过外部DMA控制器的控制,方便系统集成,加快该主控器与系统内存之间的数据交换。该主控器的物理接口端提供满足UTMI+接口规范的接口,通过与PHY相连,可以直接与外设进行通信。图1为该主控器的系统结构框图,图中主控器的列表处理器模块是系统中主要的控制器,其包含多个状态机用来处理规范中描述符定义的内容。

2 验证仿真系统介绍

2.1 使用传统平台验证USB主控器的不足

USB主控器真实的工作环境需要有硬件和软件协同配合,在传统验证平台下,从整个验证过程来看,硬件人员需要描述一套基于Verilog HDL的测试激励模拟软件环境验证其功能,之后软件人员还要再写一遍基于C程序的软件环境验证其功能,这样造成工作的重叠。同时传统验证平台使用Verilog HDL编写,抽象层次较低,在描述高抽象结构(如USB的描述符的数据结构)时比较复杂,而使用抽象层次更高的C语言会相对简单。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码