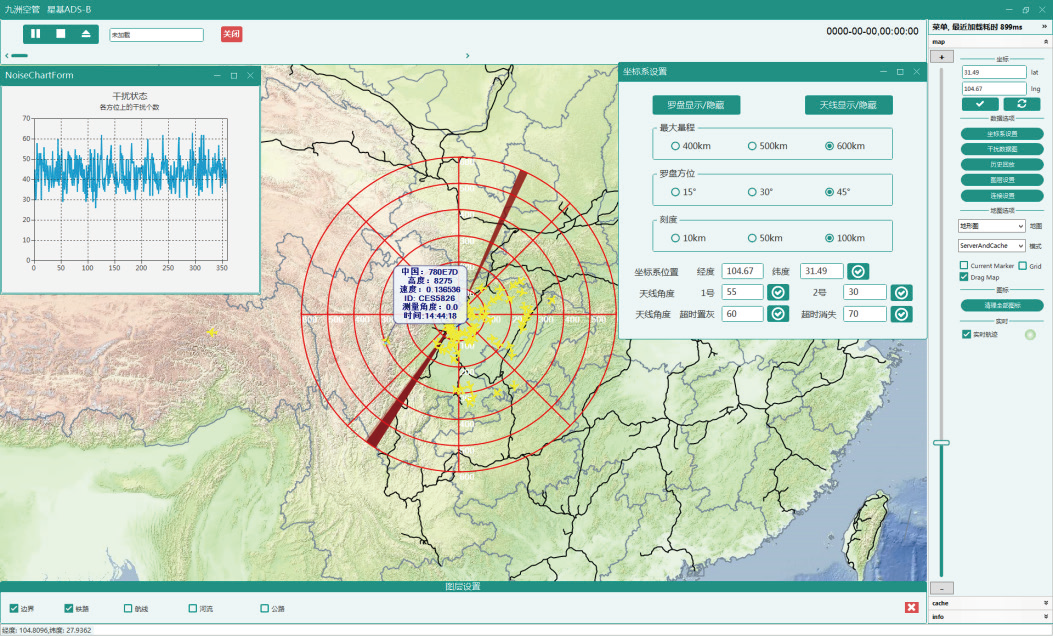

微机保护控制接口的CPLD抗干扰设计

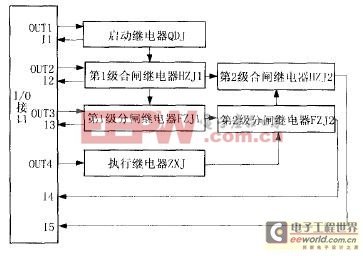

图1 继电保护控制出口原理

因此,继电保护控制出口的闭锁和冗余度设计是防止控制出口误动的关键所在。严格监视分合闸多重命令的执行顺序,不允许无序分合闸命令通过,是防止控制出口误动的根本措施。分合闸多重命令的有序执行,可以看作一个状态变化序列,用CPLD状态机对这个状态序列进行监控,就能杜绝无序状态的通过,实现控制出口的无干扰控制。

基于CPLD状态机的抗干扰控制接口设计

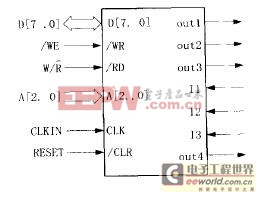

设计一个基于DSP的高压开关柜微机综合保护系统时,用一片CPLD芯片实现图1所示的I/O接口,并设计一个有限状态机,对状态输入I1,I2,I3进行监控,状态机输出作为总分合闸命令的允许和禁止信号。基于CPLD的微机保护控制接口如图2 所示。

图2 微机保护的CPLD控制接口

分合闸多重命令的状态编码

状态机有3位二进制输入,共有23=8种状态。采用二进制编码方式(Binary coded)将控制接口的初始状态S0到所有可能的状态变迁,列成一张编码表,如表1 所示。状态编码表是编写VHDL程序的基础。

表1 微机保护控制接口状态机编码表

状态机设计

状态机的时钟频率为5MHz。复位信号/Reset来自DSP微机保护装置的系统复位信号,对状态机的状态初始化。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码