高频锁相环的可测性设计

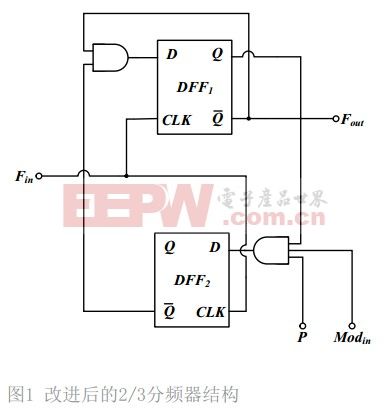

0px"> 本文将基于IEEE1149.1标准的边界扫描技术应用于模拟电路可测性设计中,对一款高频锁相环提出了测试方案,并给出了相应的测试电路。并对采用该方案进行测试的高速锁相环在增加测试电路前后电路的仿真结果进行了比较。结果表明,本文所提出的高频锁相环测试方案对锁相环本身的功能影响很小。

td. 1149.1. A Standard Test Access Port and Boundar y Scan Architecture[J].IEEE,1993

参考文献

1]Prashant Goteti,Giri Devarayanadurg, Mani Soma? DFT for Em bedded Chargepump Systems Incorporating[J]. IEEE1149.1IEEE,1997, C ustom Integrated Circuits Conference, 1997:210-213

2]IEEE S

3]Michael L Bushnell, Vishwani?Agrawal Essenentials of E lectronic Testing for Digital, Memory and Mixedsignal VLSI Circuits[M].Kluwr Aca demic Publishers, 2000

4]于宗光.IEEE 1149.1标准与边界扫描技术[J].电子与封装,200 3,3(5):40-47.

5]成立,王振宇,高平,等.VLSI电路可测性设计技术及其应用综述[J].半导体技术,2004,29(5):2024.

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码