高频锁相环的可测性设计

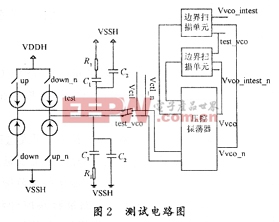

在压控振荡器的控制信号处设置开关,开关闭合时,锁相环处于正常工作模式;开关打开时 ,锁相环处于测试模式。在测试模式时,Vctl和Vctl_n是输入信号,控制VCO的振荡频率,同时利用边界扫描单元测量振荡频率,调整输入控制电压的大小,就能测量VCO的振荡频率范围。正常工作模式时,Vctl和Vctl_n是输出信号,其电压值就是电路正常工作时VCO的控制电压,测量该信号就能推算锁相环实际的输出频率大小和范围。

锁定时间的测试必须要求电路完成锁定过程才能测量,因而相对较慢。在电路正常工作时, VCO的控制信号Vctl和Vctl_n是输出信号,观察该信号是否稳定就能判断环路是否达到锁定状态。测量控制信号从不稳定到稳定的时间差就是锁相环的锁定时间。

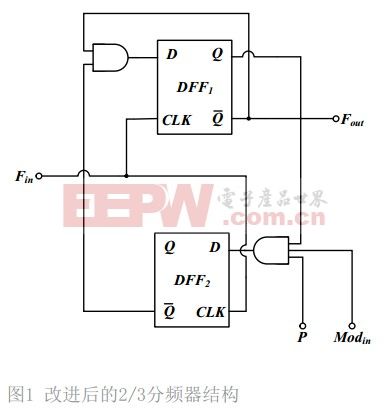

3.2 边界扫描电路

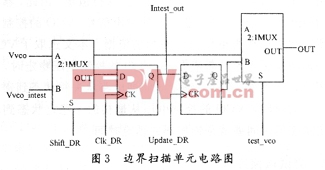

边界扫描单元电路如图3所示。Vvco是VCO的输出信号,Vvco_intest是边界扫描的测试矢量输入,test_vco是VCO的测试模式选择信号,shift_DR,clk_DR,update_DR都是边界扫描单元要求的时钟或控制信号。这些信号与集成电路中的边界扫描控制信号配合使用即可。相应另一个边界扫描单元的信号也与此类似,只是VCO的输入输出取相反信号。

锁相环正常工作时,边界扫描只相当于一条连线;在测试模式时,VCO的振荡环路被打开, 测试信号从边界扫描电路输入,经过VCO后再从输出端输出,检测这些信号在VCO内部的延迟 Tdelay,就能推算出VCO的振荡频率。该延迟是VCO控制电压的函数,扫描控制电压的值就可得到VCO的工作频率和振荡范围。

边界扫描单元的工作用IEEE1149.1标准中的Intest指令来完成。Intest指令借助于一个测试矢量来进行内部扫描测试。一旦该指令被装载到指令寄存器,测试矢量信号(VCO的输入信号Vvco_intest 和Vvco_intest_n)就被存储于边界扫描单元中的扫描寄存器,经过各级延迟在VCO输出端输出[2]。

4 仿真结果

理想的测试电路既可以有效地测试电路性能又不影响电路的正常工作。锁相环作为时钟发 生器,需要给大规模电路提供稳定的时钟信号,因此影响锁相环性能的测试方案是不可取的。

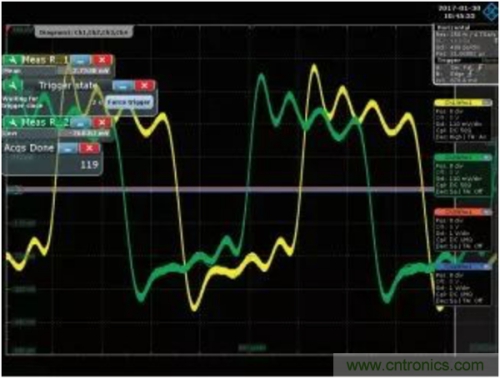

为了检测本文所述的边界扫描测试方案的有效性,对增加测试电路前后的锁相环电路网表分别进行了Hspice仿真,如图4所示的波形是增加测试电路前后锁定时锁相环的输出波形图。

由图4看到,对1 GHz的高频输出,增加测试电路后信号周期没有明显变化,经测量两者最大相位差为25 ps。由测试电路仿真结果可以看出,该测试方案对原锁相环的功能特性影响不大,是有效可行的。

5 结语

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码