基于KeyStone DSP的多核视频处理技术

2.4 多内核间的协作与同步

当多个内核处理同一视频通道时,这些内核之间必须相互通信,才能实现对输入数据的同步、分离或共享,合并输出数据或者在处理过程中交换数据。附录 A - 解码器性能依赖阐述了将视频处理功能划分成多个内核的几种算法。

并行处理法和流水线处理法是两种常用的分区算法。并行处理的范例是两个或两个以上的内核可以处理同一输入通道。必须有一个不受竞态条件影响的机制在多个内核之间共享信息。可将信号标用来保护全局区域免受竞态条件的干扰。硬件需要支持阻塞性和非阻塞性信号标,以有效消除竞态条件,即消除两个内核同时占用同一存储器地址的可能性。

如果使用流水线算法,一个或一个以上的内核可执行运算的第一部分,然后再将中间结果传递第二组内核继续处理。由于视频处理负载取决于处理的内容,因而这种传递机制可能面临如下问题:

- 如果一个以上的内核处理流水线的第一阶段,那么第 N+1 帧可能先于第 N 帧被处理好。因此该传递机制必须能够对输出/输入进行排序。

- 即使流水线上的各内核总体是均衡的(在处理负载方面),但个别帧未必如此。该传递机制必须在不同的流水线阶段之间提供缓冲,以使内核没完成工作时不至于影响其他内核停滞等待。

- 如果算法要求流水线的两个阶段间能稳固实现紧密的链接(例如,为解决依赖性的问题),则该机制就必须能够支持紧密链接与松散链接。

2.5 多芯片系统

实时处理超级视频 (SVGA)、4K 及更高分辨率,或处理 5 级 H.264HP可能需要不止一个芯片一起协作。要构建一个具有超高处理能力的双芯片系统,拥有可连接两个芯片的超快速总线至关重要。

第三部分描述了可满足上述所有要求及难题的 KeyStone系列 DSP架构。

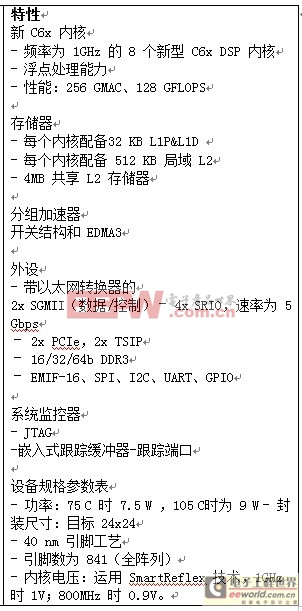

3.KeyStone DSP – TI 最新多内核处理器

TI KeyStone 架构描述了广泛应用于视频处理等要求高性能和高带宽的系列多内核设备。图 2 对 KeyStone DSP进行了概括性描述。本章针对在第二部分中阐述的视频处理硬件要求对 KeyStone DSP 特性进行了介绍。

图 2 KeyStone DSP 方框图

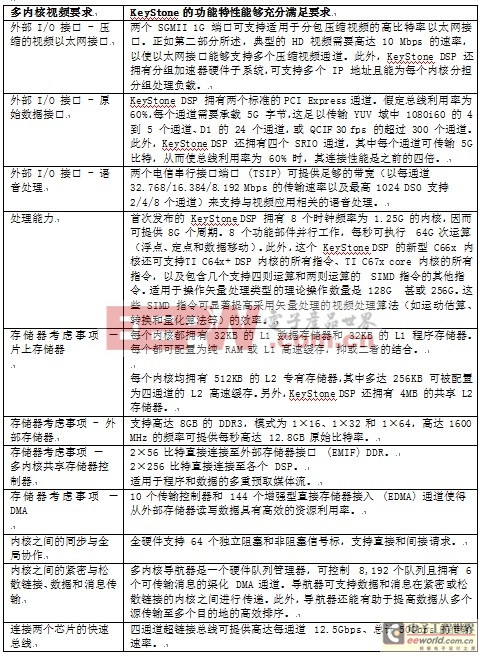

表 1 说明 KeyStone DSP 如何满足视频处理要求。

附录A - 解码器性能相关性

编码器所采用的工具和算法以及视频内容都会影响解码器的性能。下列因素将影响解码器性能:

- CABAC 或 CAVLC 熵解码器的选择

- 跳帧的数量

- 帧内预测模式的复杂性

- 预测类型—运动估算或帧内预测。(运动补偿需要消耗的解码周期数不同于帧内预测补偿。采用运动补偿还是帧内预测取决于编码器。)

- 不同的运动估算工具(每个宏模块一个运动矢量,每个宏模块 4个运动矢量,或每个宏模块 8 个运动矢量)能改变解码器的复杂度和周期数。

- B 帧宏模块的运动补偿涉及两个参考宏模块,并消耗更多周期。

- 媒体流中的运动量不仅会更改跳过宏模块的数目,同时还会改变解码器的处理要求。

- 比特流在运动矢量、模块值、标记等各个不同值等之间的分配取决于媒体流的内容和编码器算法。不同的分配会相应改变熵解码器的周期数。

附录B — 运动估算和速率控制

运动估算是 H.264 编码中很大一部分内容。H.264 编码器的质量取决于运动估算算法的质量。运动估算所需的周期数取决于运动估算算法的功能特性及特征。以下是几个影响运动估算周期消耗的主要因素:

- I 帧、P 帧和 B 帧的频率

- L0(对于 P 帧和 B 帧)和 L1(对于 B 帧)中的参考帧数目

- 搜索区域的数目

- 搜索区的大小

- 搜索算法

良好的运动估算算法可能消耗总编码周期的 40-50%,乃至更多。

速率控制算法是影响编码质量的主要因素。为了最大限度地提高视频的感知质量,智能速率控制算法可在宏模块和帧之间分配可用的比特。

部分系统可执行多重处理通道,以便在宏模块之间更好的分配可用比特。多条通道虽然能提高感知质量,但却要求更密集的处理。

附录C - 外部存储器带宽

由于运动估算算法的原因,编码器通常比解码器需要更高的内部带宽。编码器的要求分两种情况计算:低比特率 QCIF 和高比特率的 1080p。

- 第一种情况 -- QCIF 264 BP 编码器:

两个完整的 QCIF 帧能驻留在高速缓存或 L2 乒乓缓冲器中。每个帧需要的容量不到 40 KB。采用一个参考帧对某一帧进行编码时,系统应为每次 QCIF 处理传输 80KB 的数据,并输出少量数据。200 个15 fps 的 QCIF 通道所需的总内部带宽为:

80KB * 15 (fps) * 200(通道数)+ 200(通道数)* 256/8 KB(QCIF 通道的输出比特率)= 240MB + 6.4MB = 250MB/s

- 第二种情况 -- 1080p 60 H.264 HP:

假定采用最差情况中的算法来执行运动参考帧的运动估算,该参考帧可能需要从外部存储器移至内部存储器多达三次。此外,也可假定采用多达四个参考帧的高级算法。因此,单个 1080p60 通道的运动估算是:

3(复制 3 次)* 1920*1080*1(在运动估算中,每像素仅 1 个字节)*60 (fps) * 4(参考通道) = 1492.992 MBps

是否移动可进行处理和运动补偿的当前帧由以下情况来确定:

2(当前帧和运动补偿)* 1920 * 1080 * 1.5(字节/像素)* 60 = 373.248 MBps

综上所述,以上两个汇总结果规定了输出比特流。一个通道的总和为1866.24 MBps,即两个 H.264 HP 1080p60 编码器为 3732.48 MBps,这意味着约占用外部存储器原始数据带宽的 30%。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码