高阶QAM调制器的设计与实现

DDS系统输出信号的频率为f0=fclk×M/2N,频率分辨率为△f=fclk/2N,当M=2N-1时,DDS最高的基波合成频率为f0max=fclk/2。对于本系统,时钟频率fclk=155.520 MHz,N取12。仿真结果如图4所示。

4 系统设计与仿真

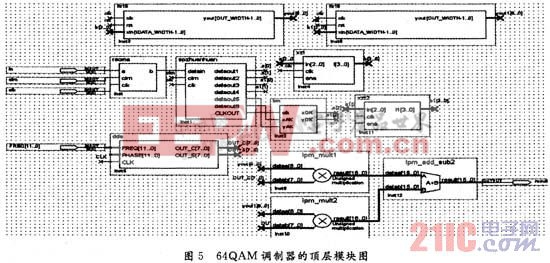

根据以上各模块单元的设计,构成64QAM调制器的顶层文件如图5所示。运用QuartusⅡ及Matlab软件实现64QAM调制器仿真,仿真结果如图6所示。

仿真可以按不同原则分类:①按所用模型的类型分为物理仿真、计算机仿真、半实物仿真;②按所用计算机的类型(模拟计算机、数字计算机、混合计算机)分为模拟仿真、数字仿真和混合仿真;③按仿真对象中的信号流分为连续系统仿真和离散系统仿真;④按仿真时间与实际时间的比例关系分为实时仿真、超实时仿真和亚实时仿真;⑤按对象的性质分为宇宙飞船仿真、化工系统仿真、经济系统仿真等。

5 结 语

本文介绍了用FPGA实现全数字高阶QAM调制器的思想和方法,采用原理图和Verilog语言,用可编程芯片StratixⅡ系列中的EP2S30F484C3实现了整个设计,结果表明符合设计要求。为进一步的研究和设计全数字高阶QAM系统打下了良好的基础。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码