图像的二维提升小波变换的FPGA实现

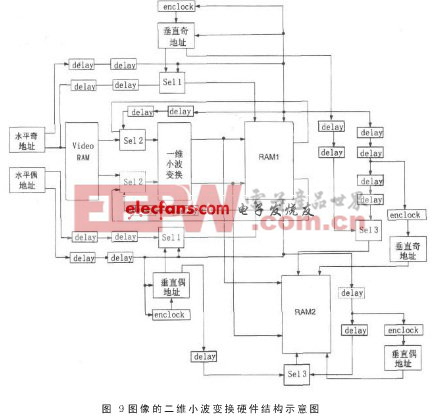

系统顶层原理如图9所示(图中略去了时钟信号控制线)。在系统结构中添加delay延时寄存器,从调整系统的时序;RAM1、RAM2是没有被放入初始化文件的两个相同的存储器;sel1、sel2、sel3是三类相似功能的数据选择器,完成整个结构的基本控制功能。sel1实现的功能是当行变换结束后,切换RAM1的地址输入为列方向地址;sel2实现的功能是当行变换结束后,将“小波变换”模块的输入数据从行变换地址寻址得到的数据切换到列变换地址寻址得到的数据;sel3实现的功能是通过行变换标志信号和列变换标志信号来实现对RAM2的读写控制,当系统进行列变换时,RAM2模块写无效;当系统进行列变换时,RAM2模块写有效;当列变换完成时,RAM2模块再次写无效,此时RAM2中已经写入数据。

系统工作过程如下:首先是行方向一维小波变换:图像的灰度值数据预存在“Video RAM”模块中,时钟信号一来,便立即启动水平奇地址模块和水平偶地址模块,开始奇偶地址分裂,进行行方向的一维小波变换,同时将行变换的数据存到RAM1中。其次再进行行、列变换切换时控制:当一次行方向地址奇偶分裂一结束,水平奇地址模块和水平偶地址模块将发出一个结束的标志信号,它将启动sel1、sel2、sel3开始工作。最后再进行列变换的过程,RAM2中存储列变换的结果数据。此时即完成了图像二维提升小波变换。

采用QuartusⅡ软件对系统进行了综合、仿真,系统在FPGA芯片中(EP2C70F672C6)实现,结果显示系统耗时为163.85μs。完全能够保证图像压缩系统的实时性要求,它的值正是二维小波系数。

本文分析了提升算法的系数分布存在的特点,提出了5/3二维提升小波变换硬件实现的简化方案,并在FPGA芯片中实现了对图像的5/3二维提升小波变换。采用FPGA芯片实现计算量十分复杂的二维提升小波变换,可以大大提高图像压缩的运算速度,保证系统的实时性要求。本方法在很多领域的图像处理中有着广阔的应用前景。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码