图像的二维提升小波变换的FPGA实现

在提升算法的实现中,它的系数分布存在的特点,可以简化设计的实现。

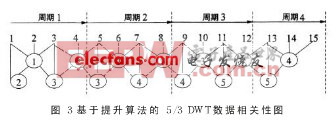

(1)对输入数据的处理,只牵涉到了两两相邻的数据(圆圈中的数字表示执行的时钟序号),数据相关性图如图3所示。对图像数据进行行/列变换时,只需要得到该数据以及同一行(列)的相邻两个数据,就可以进行当前数据的行/列变换,而与其他数据无关,其本质是将奇序列数据与偶序列数据顺次逐一输入。因此,对数据输入部分的处理可以通过构建两个地址生成模块,实现对奇偶地址数据的读取。

(2)提升算法具有原位计算的特点,因此计算的系数可以直接替代原始数据而不需要附加数据存储空间。对于它的行、列变换都可以只使用同一个存储器RAM进行原始数据、中间数据和变换后数据的存储。由图4可以清楚地看到,二维提升小波变换后的系数在存储空间的分布情况。原位存储的特点大大地节省了片上资源,最有效地提高了系统利用率。

(3)行方向与列方向的提升小波变换是一样的,因此可以将一维提升小波变换设计成一个独立的模块,之后对它进行反复调用。这也是简化系统的有效途径之一。

3 图像的二维提升小波变换的总体设计

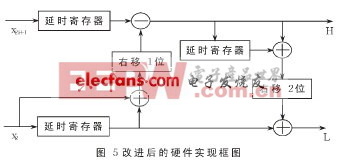

一维小波变换是二维小波变换的前提,对于它的FPGA实现,由图2可以看出,5/3提升小波变换中主要计算是加、减运算,而除法运算是除以2和除以4,这在硬件实现中可通过“右移”操作实现快速运算。因此在设计中只需将图2中的乘法器模块用相应的移位操作模块代替。而图2中乘以-1/2模块被替代为右移1位模块之后,便少了一个负号,因此再将此乘法器后面的加法器模块改为减法器,同样达到了乘以-1/2的效果。这样的改进还简化了负数在硬件电路中的运算。改进后的硬件实现框图如图5所示。

二维小波变换的硬件原理结构如图6所示,其工作原理如下:采用RAM1功能模块来实现图像数据的存储;通过地址生成模块来实现对存储器中奇偶地址数据的分裂操作,先进行行方向的奇偶序列地址分裂,并做一维小波变换;行方向的操作一结束,立即进行列方向的奇偶序列地址分裂,并做一维小波变换。以上两步反复进行,便可完成图像的多级二维小波变换,最终的小波变换系数将被存储在RAM2中。

4 二维5/3提升小波变换的FPGA实现

4.1 主要功能模块的设计

(1)RAM模块。要实现对同一个数据块的双输出,以便进行一维提升小波变换,因此选择了具备双端口功能的宏模块,用来存储行小波变换系数和存储列小波变换系数,这样的结构能更加清晰地反映算法的实现流程,能够实现算法中对奇偶地址数据的同时读取。

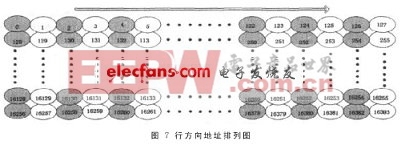

(2)行方向奇地址发生模块和行方向偶地址发生模块。行方向奇地址发生模块实现功能是在每个时钟周期内,依次输出如图7所示的白色圆圈所示存储器行方向奇数单元的地址,这实际上是一个计数功能。行方向偶地址发生模块实现的功能与行方向奇地址发生模块类似,不同的是在每个时钟周期内按行输出图7所示的灰色圆圈的序号。

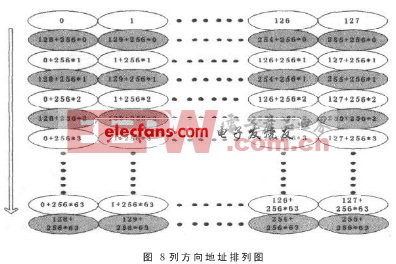

(3)列方向奇地址发生模块和列方向偶地址发生模块。在计数结束时,列方向奇地址发生模块在每个时钟周期内依次输出如图8所示的白色圆圈所示的存储器列方向奇数单元的地址。列方向偶地址发生模块实现的功能与列方向奇地址发生模块类似,不同的是在每个时钟周期内按列输出图8所示的灰色圆圈的序号。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码