基于FPGA高速并行采样技术的研究

2.2 增益误差的计算和校正

在本文的设计中,经过模拟前端多相时钟电路设计,时间相位误差可以忽略,且ADC的基准电压由同一电源供电,偏置误差也可忽略,在此,利用DFT变换校正增益误差。对于只有增益误差的第k个子通道的输出信号yk(n)=gkAcos[2πfin(mn+k)/fs+θ],做N点DFT得:

,因此,经过增益误差校正输出信号为:

3 实验仿真结果

图5是经过FPGA内部映射之后的时序仿真图,可以看到经过精心设计的多相时钟技术以及合理的同步接收使信号的采集效果良好。

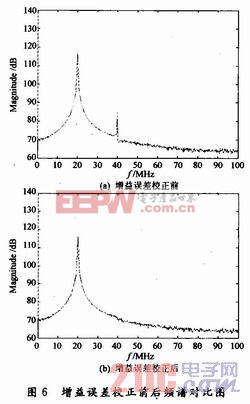

图6是采集得到的数据经过增益误差校正前后的频谱对比图,可以看到在40 MHz处,杂散得到了明显的抑制。其中,模拟输入信号的频率为20 MHz。

4 结语

针对高速并行ADC时间交叉采样技术对多相时钟信号的高要求以及采集数据的误差,介绍了多相时钟设计的一种方法和利用FFT技术实现对增益误差的校正。通过实验仿真证明,该设计能够有效提升数据采集系统的性能。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码