基于FPGA高速并行采样技术的研究

1.3 数据接收和存储

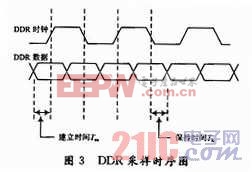

ADC输出数据速率为400 MHz,与之相对应的随路时钟为200 MHz,利用DDR方式接收数据。FPGA内部PLL产生的四路时钟信号的上升沿和下降沿都对输入数据进行实时采样,数据与采样时钟之间保持一定的相位差,以满足同步时序的数据建立时间(Tsu)和保持时间(Th),如图3所示。

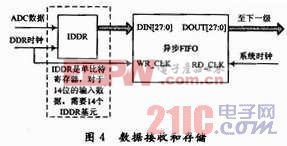

通过FPGA输入模块IDDR映射生成内部寄存器接收数据,并由异步FIFO实现内部时序同步和存储。ADC采样数据的有效位是14 b,利用FPGA软核生成的FIFO宽度和深度可分别设置为28 b和128,其中高14位[27:14]存储奇数时刻的采样数据,低14位[13:0]存储偶数时刻的采样数据,数据存储如图4所示。

2 数据预处理

2.1 时间交叉采样引起的误差

在图1所示的多通道并行时间交叉采样的数据采集系统结构中,各个子通道间数据不可能完全匹配,主要会产生三种误差:

(1)由于各个子通道ADC的增益不一致而引起的增益误差(Gain Error);

(2)多相时钟设计不完全理想以及PCB板线路走线延迟不一致引起的采样时刻偏离带来的时间相位误差(Time Skew Error);

(3)各通道ADC基准电压不一致而引起的偏置误差(Offset Error)。

以正弦信号为例,令输入信号S=Acos(2πfint)+θ。其中:A,fin,θ分别为输入信号的幅度、频率和初始相位。若系统总采样率为fs,经m片ADC时间交叉采样后第k个子通道的输出为:

![]()

式中:0≤nN-1,N为每个子通道数据采样点数;gk为第k个子通道的增益;δ为时间误差;σ为偏置误差。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码