一种低功耗64 倍降采样多级数字抽取滤波器设计

这种非递归结构所需要的1 位寄存器总数为R=1+2+3+?+20=210,而等效功耗因子P=(2+3+4+5+6)×16+(7+8+9+10+11)×8+(12+13+14+15+16)×4+(17+18+19+20+21)×2=1 130。与经典结构相比,寄存器总数相等,但功耗减小到原来的1/ 6,采用这种非递归结构不但改善了系统稳定性,还大大提高了系统性能。由于电路实现时需采用层叠结构,5级结构即需5 级层叠,如果其中有一级为4 或者更小,那就可以减小层叠数,从而进一步减小硬件和功耗。

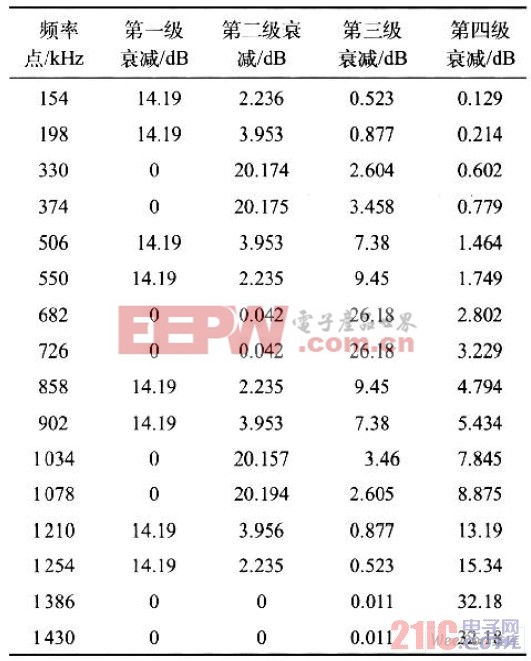

阻带衰减为衡量CIC 滤波器性能的一个重要指标。通过牺牲部分阻带衰减性能可减小层叠数。对于4 级结构,应分别考虑各级在需要的衰减频段处能达到的衰减值。在Matlab下分别仿真(1+z-8)、(1+z-4)、(1+z-2)、(1+z1)的幅频特性,并依次设为第一级到第四级。设CIC 滤波器的零点为FZ,根据设计指标,中心频率fC=22kHz,只要在所有FZ ± fC频率范围内阻带衰减值能达到80dB,CIC滤波器即可满足设计指标要求。由于最小衰减值出现在FZ-fC 与FZ+fC 关键频率点处,在Matlab 下仅测试单级时关键频率点处的阻带衰减,结果如表1 所示。

表1 各级为单级时在关键频率点处的阻带衰减值

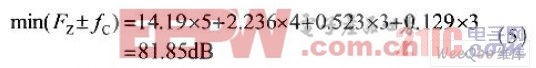

通过计算,当第一级到第四级的级联级数分别减小为最低的5、4、3、3 时,则最小阻带衰减量计算为:

虽然以上降低层叠数的改进结构其最小阻带衰减满足设计要求,但后级补偿滤波器无法使纹波达到设计要求,应加大其中一级或两级的级联级数来降低补偿后的通带纹波,将级数增大后纹波的变化如表2 所示。

表2 级数增大后补偿结果的变化

只有当级联级数为3、4 、5 、5 时补偿后的结果接近设计指标要求。将补偿后的整体幅频特性沿着Y 轴方向向下移动约0.008dB 左右,这样最大纹波为0.016 2-0.008=0.008 2dB,最小纹波为-0.000 37-0.008=-0.008 37dB,这样纹波就在指标范围内,所以采用这种级联方式可以满足设计指标要求。最终确定的CIC 滤波器系统函数为:

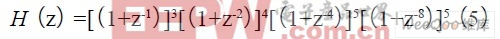

图4 为改进前后CIC 滤波器的幅频响应,实线与虚线分别对应为改进前后的幅频响应,改进后的曲线比改进前有明星的上升,部分点处上升的幅度还较大。但由于改进后在关键点处能够达到衰减的性能要求,牺牲其他非关键点处的衰减特性以降低硬件资源和功耗的设计策略还是非常可取的。

图4 改进前后的幅频响应比较

此时,寄存器总数降低到R=1+2+3+?17=153,等效功耗因子P 降低为P=(2+3+4)× 16+(5+6+7+8)×8+(9+10+11+12+13)×4+(14+15+16+17+18)×2=732,比未改进前少用了57 个寄存器,功耗则降低了35%,在保持纹波性能的前提下,硬件资源消耗和功耗明显降低。

4 补偿滤波器与半带滤波器设计

改进后的CIC 滤波器幅频特性整体向上偏移,导致通带频率处的各点频率向上移动,与改进前幅度相同的点在改进后的曲线上必然向前移动,即改进后的频率点相当于左移。所以,针对改进后的CIC 滤波器设计补偿滤波器时,其通带截止频率点相应地也要左移。若将通带截止频率设为小于20kHz 的点,通过调整参数以优化补偿后的纹波性能,即调整幅频特性曲线后最终得到的通带纹波为±0.006 2dB。

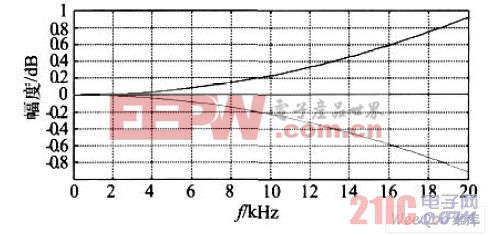

补偿前后的通带特性如图5 所示,图中下方曲线为CIC 滤波器在通带范围内的幅频响应,上方曲线为补偿滤波器的幅频响应,中间部分为补偿后的幅频响应。显然,经补偿后的曲线在通带范围内变得更加平坦。

图5 补偿前后的通带幅频特性

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码