基于多相滤波的数字接收机的FPGA实现

2 宽带数字接收机的FPGA硬件实现

2.1 系统模块实现

设计在Xilinx公司的XC4VSX55单片FPGA上实现,包括串并转换模块、多相滤波模块、信号检测模块、数据选择模块、瞬时测频模块以及PDW形成模块,如图8所示。

(1)串/并转换模块主要功能是降低数据速率,进行并行处理,原始采样速率为2 000 MSPS,分成D=16路并行数据,每路数据速率变为125 MSPS。

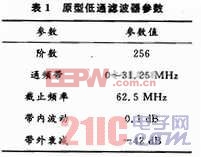

(2)多相滤波模块的功能是实现高效的多相滤波结构。它由两级乘法器、有限冲击响应滤波器(FIR)和16点并行FFT组成。其中,第一级乘法系数随着数据的先后次序,并按1,1,-1,-1的顺序变化来改变相应数据的符号。FIR滤波器采用全并行结构设计,原型低通滤波器的性能见表1。将原型滤波器分成16路,每相滤波器16阶。第二级乘法器为一复数乘法。16点全并行FFT,采用流水线结构,可以在一个时钟节拍内完成FFT运算的功能。

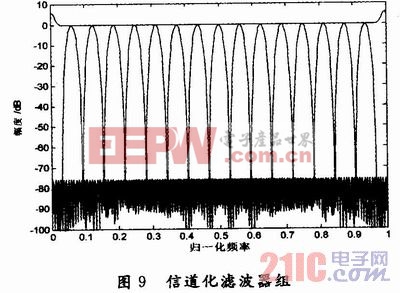

(3)信号检测模块的功能是对某一信道是否有信号进行判断。多相滤波出来的信号为复数,可以对其取模,利用幅度进行门限检测,同时可以测量到达时间和脉冲宽度。由于滤波器的暂态特性,脉冲信号通过滤波器组会产生“兔耳效应”,为了消除兔耳效应以及噪声的影响,在每个信道门限检测的后面加了一个最小脉宽检测电路,把兔耳效应和噪声引起的窄脉冲剔除掉,如图9所示。

(4)数据选择模块功能是将有信号信道的数据选出来,为后面的测频做准备。不必在每个信道后面都接一个测频模块以减少后面的测频模块,节约芯片资源。

(5)瞬时测频模块功能是运用Rife算法估计检测到信号的瞬时频率,并消除镜像信号的影响。根据门限检测的到达时间,选取N点数据做FFT,左右各删除N/4点,只取中间的N/2。对这N/2点做Rife插值,若最高谱线大于某固定值时,可以判断该信道存在真实信号,否则为虚假信号。

(6)脉冲描述字形成模块是将上述截获的脉冲信号的到达时间、脉冲宽度和瞬时频率的参数编码信息用PDW的形式输出。

2.2 仿真验证

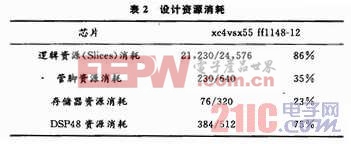

经过在ISE中编译、综合、布局布线得到FPGA资源使用报告如表2所示;数字信道化接收机实现参数如表3所示。

3 结语

将理论算法和FPGA实现结合起来,分析了数字信道化的原理,提出了一种基于多相滤波的信道化接收机与Rife瞬时测频相结合的方法。这种方法实现了大带宽的全概率接收,可以消除虚假信号,同时提高测频精度。整个接收机在单片FPGA中实现,采用并行和流水线操作,可实现实时检测,生成脉冲描述字(PDW)。在信道化接收机的数字化、软件化和小型化发展方面具有重要的现实意义。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码