基于多相滤波的数字接收机的FPGA实现

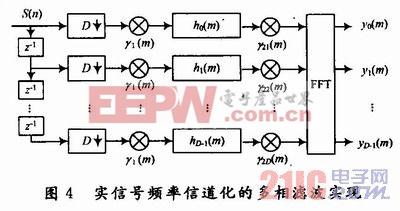

这样得到实信号数字信道化的多相滤波实现模型如图4所示。

1.3 算法仿真

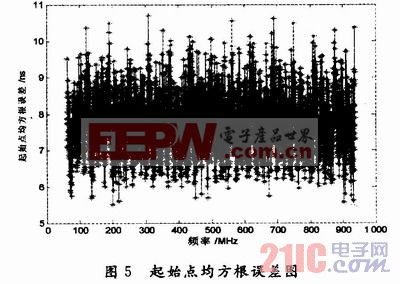

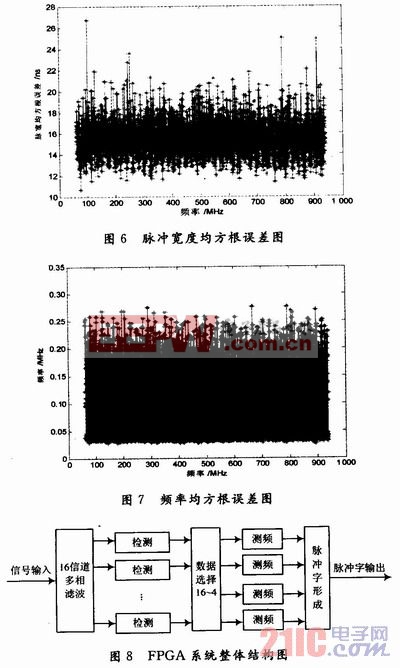

仿真时,设信号的采样频率为2 GHz,信道带宽为62.5 MHz,共16个信道,输入信噪比为0dB。输入信号样本为1 920点(每个信道120点),信号的起始点为112 ns,脉冲宽度为600 ns。在62.5~937.5 MHz间对起始点、脉宽和频率进行测量,频率步长为250 kHz,参数的均方根误差如图5~图7所示。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码