基于FPSLIC设计的DES解密和AES的分组加解密的实现

2.3 器件编程与试验验证

1.将下载电缆ATDH2225的25针的一端从计算机的并行口接出,令一端10针扁平线插入ATSTK94实验板的J1插头上。下载电缆的标有红色的线和J1插头的第一脚连接。

2.因为要和计算机串口进行通信,因此要制作一个串口连接电缆,其九针连接电缆的连接关系如下图2-2。电缆一端连接在计算机的任意串口上,另一端连接在实验板上的UART0上。连接电缆只需要连接三根线,UART0的2端连接在FPSLIC的发送端,因此它和计算机的串口2端(接收数据端)相连。UART0的3端连接在FPSLIC的接收端,因此它和计算机的串口2端(发送数据端)相连。

3.选择4MHz时钟,即在实验板上将JP17设置在靠近板子内侧位置,而将JP18不连接,也就是将其连接跳线拔掉。

4.将直流9V电源接头插入ATSTK94实验板的电源插座P3上。

5.将实验板上的开关SW10调至PROG位置。开关SW10有编程(PROG)和运行(RUN)两种连接。在编程位置,用户可以通过下载电缆和下载程序软件CPS,将SystemDesigner生成的FPSLIC数据流文件给配置存储器编程。在运行位置,FPSLIC器件将载入数据流文件并运行该设计。

6.打开电源开关SW14,即将它调整到ON位置。这时候实验板上电源发光二极管(红色)发光,表示实验板上已经上电。这样,硬件就连接完毕,等待下一步的数据下载。

7.单击OK按钮,即生成数据流文件,它将下载到ATSTK94实验板的配置存储器中,这时,Atmel的AT17配置可编程系统(CPS)窗口被打开,如下图2-3,并自动给器件编程。

图2-3FPSLIC控制寄存器设置对话框

在Procesure下拉列表框中选择/PPartition,ProgramandVerifyfromanAtmelFile。在Family下拉列表框中选择AT40K/Cypress,在Device下拉列表框中选择AT17LV010(A)(1M)。其余采用系统的默认值。然后点击StartProduce按钮,如果电缆等硬件设置正确,那么程序将下载到实验板上。

8.将开关SW10调至RUN位置,打开串口调试程序Accesspot129软件。对于Accessport129的设置为:串口为COM1(根据用户选择的计算机端口来设定),波特率:9600,校验位:NONE,数据位为8,停止位选择1,串口开关选择开;

3 试验结果:

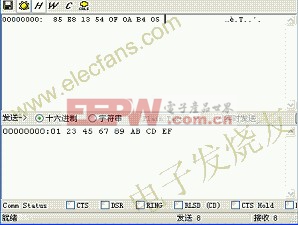

图3-1中,下面方框中是要输入的64比特的明文,(程序中输入的明文为0123456789ABCDEF),当这64个比特的数据全部输入完毕后,点击发送按钮,在软件上方的数据接收端显示出经过DES算法加密后的密文(85E813540F0AB405)。通过硬件实现的的结果和实际仿真结果是完全一致的。同时通过数码管也分别显示出最后的加密数据。至此整个硬件试验结束。

图3-1Accesspot串口调试软件显示的结果图

从上面的串口调试软件可以看出,DES算法的仿真是正确的也是可以在实际中应用的。同理,可以通过以上的方法来实现DES解密和AES等其它的分组加解密。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码