一种基于FPGA的数字复接系统的设计与实现

数字复接系统的FPGA设计

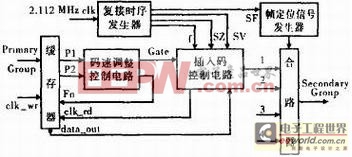

本次FPGA设计采用分层设计,顶层为整个系统的原理框图(见图3),用一些符号表示功能块,然后把每个功能块分成若干子模块,各模块独立设计。下面就各模块的设计思想进行详细介绍。

复接电路设计

复接电路如图4所示,它由复接时序发生器、缓存器、码速调整控制电路、插入码控制电路、帧定位信号发生器和合路器6个模块构成。图中只画了第一条支路参与复接的实现过程,因为四条支路的过程完全相同,因而略去其余3个支路的电路。

图4 复接电路框图

(1)复接时序发生器模块

输入为2.112MHz频率的均匀时钟,通过该模块产生插入码控制电路所需的插入标志时隙脉冲SZ、调整插入时隙脉冲SV、频率为2.112MHz的非均匀时钟f(从输入的均匀时钟扣除了时隙SZ和SF)和帧定位信号发生器所需的时隙脉冲SF。

(2)缓存器模块

基群信号以2.048MHz的均匀时钟clk_wr写入缓存器,同时以2.112MHz的非均匀时钟clk_rd读出,clk_rd由插入码控制电路产生。该模块还需输出每次写入和读出一帧数据时第一个clk_wr脉冲P1和clk_rd脉冲P2,送给码速调整控制电路模块。在该模块的设计中,应注意每一帧信息码的位数不是固定的,必须通过码速调整控制电路模块的反馈信号Fn来确定,当反馈信号表明本帧需要调整,则位数为205;反之,位数为206。

(3)码速调整控制电路模块

缓存器的写入脉冲超前于读出脉冲的时间量称为读写时差,读写时差的大小总随时间不断变化着。该电路中缓存器的写入速率低于读出速率,随着时间的推移,缓存器中所存信息码数目越来越少,最后导致“取空”而造成错误的数据传输。因此,我们必须设定一门限,当信码数降到门限值时,就进行码速调整。

通过对各时刻读写时差的联系以及趋向最终状态变化的分析得出,读写时差的最低点总是发生在一帧末尾,而在帧首通过两脉冲相位差就能判断本帧是否需要码速调整。具体地说,P1和P2输入进行鉴相判决得到帧首的读写时差T0,与调整门限值TS进行比较,若T0>TS则本帧不需要调整,反之若T0≤TS,则需要调整。这时模块输出反馈信号Fn给缓存器,和调整控制负脉冲Gate给输入码控制电路模块。

(4)插入码控制电路模块

该模块的功能是对缓存器的读出信息进行插入码控制,输出2.112MHz的非均匀时钟clk_rd和参与合路的支路码流。为了标志是否在时隙SZ有插入调整比特,就必须引入插入标志码。通常在一帧中规定一个特定时隙SV,提供一次码速调整的机会。如果某支路需要进行调整,就在该时隙插入一比特脉冲,如不需要调整则该时隙仍传支路信息。为确保可靠性,通常采用3位码作为插入标志码。如果某支路有插入调整,用标志码为111来表示,否则用000表示。

(5)帧定位信号发生器模块

该模块产生帧同步信号和告警指示码,帧定位信号可以集中插入,也可以分散到各支路插入,考虑到设备和延迟问题,我们选择集中插入。

(6)合路器模块

根据每个时间间隔传送码字的多少,有3种排列方式:按位复接、按字复接和按帧复接。其中按位复接要求缓存器容量较小,较易实现,而且二次群帧结构是由4个支路子帧按位复接而成,所以一般采用按位复接,本文采用的也是该方式。该模块按位顺序循环读取四路码速调整后的码流,在对应SF时隙插入帧定位信号“111101000000”,得到二次群信号,即完成整个复接部分。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码