基于FPGA的LDPC编码设计

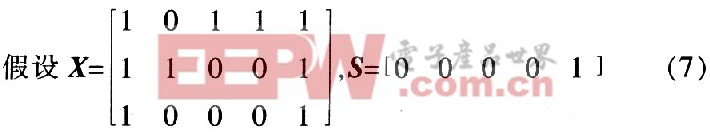

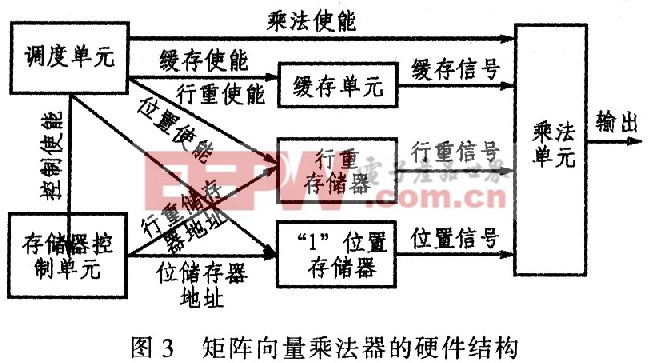

矩阵X每行中“1”的位置可看作选择向量s相应元素的地址索引,将选择的所有元素相加作和,即完成X中某行与向量的运算。由于涉及的运算都是二进制加法,相加作和操作可简化如下:根据矩阵每行“1”的位置选择向量s的元素。统计被选择的元素中“1”的个数,若结果为奇数则说明相加的结果为“l”,否则说明相加的结果为“0”。判断结果为奇数或者偶数可由其二进制形式的末位是“1”或者“0”得到。通过设置2个计数器分别计算各行行重和选择的向量s相应位置的元素中“1”的个数,即可实现乘法单元的运算。矩阵向量乘法器的硬件结构如图3所示。

从图3可知矩阵向量乘法器包括1)调度单元,产生各模块单元的使能信号;2)缓存单元,对输入信息序列进行缓存处理;3)存储器控制单元,产生存储器的地址信号;4)“1”位置存储器,存储矩阵各行“1”的位置;5)行重存储器,存储矩阵相应各行行重;6)乘法单元,进行向量乘法运算,最后输出码字。

4 结果验证

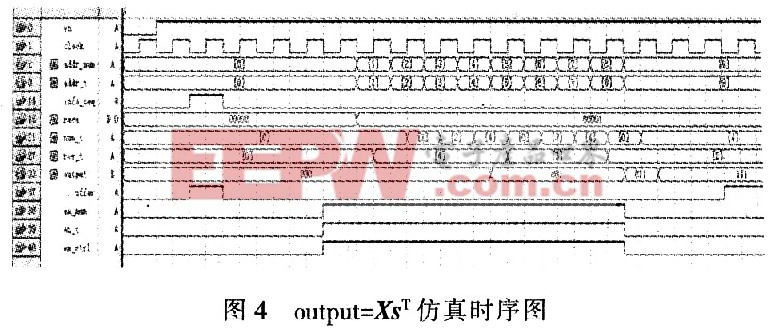

矩阵向量乘法器仿真结果验证在Qum-tusⅡ环境下,实现output=XsT,得到如图4所示的仿真时序图。图4中“en”是使能信号,“cloc-k”是时钟信号,addr_nun、adds_t分别为2个存储器的地址信号,info_seq是输入信息信号,rece是信息信号经过缓存后的输出信号,num_t是“1”在各行的位置信息,rOW_t是相应各行的行重,output是矩阵与向量相乘的结果。

由图4可知,output=[1 1 1],信号输出有一个时钟周期的延时,仿真结果正确。

5 结束语

用本文描述的方法,在1片Stratix系列的FPGAEPIS25F67217中,实现了最大码长为4 096的灵活编码方案,编码器占用约lO%的逻辑单元,约13%的存储单元,综合后时钟频率达到166 MHz,数据吞吐率达到48.33 Mb/s。该编码器结构是一种通用的设计方案,可以灵活地应用于各种不同类型的LDPC编码中,并可有效地分配存储器单元和最大可能地实现运算过程中的并行处理,但由于其采用通用的编码算法,实现的复杂度高于某些特殊结构的LDPC编码器,比如准循环LDPC码。另外通过优化时序和编码结构,可以进一步提高本文编码器的编码速度。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码