基于FPGA的LDPC编码设计

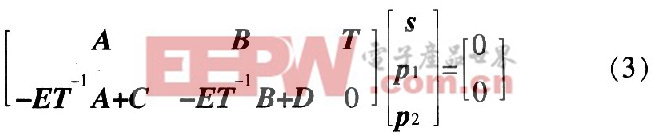

设c:[sp1 p2],其中s为系统信息部分,p1和p2共同组成校验信息部分,p1长为g,p2长为(m-g)。HcT=0左乘

得到

得到

定义F=-ET-1 B+D,并且假定F是非奇的,由式(3)可得到p1和p2的求解式分别为

在式(4)求解p1的过程中,要求矩阵F可逆,因此F必须为非奇异的,即可逆。因此实际编码前必须进行秩校验。为得到F,对原始H矩阵进行高斯消元得到式(6)的形式:

如果F为奇异的,则将F中的列与其最左边的列进行交换,直到F非奇异为止。

编码复杂度主要由g×g维矩阵F-1与向量(-ET-1 A+C)sT相乘决定。RU算法在g很小时,即g2n时,编码复杂度与码长n成线性关系。因此,为了进行有效编码,预处理要使得g应尽量的小。

2.2 编码器硬件结构

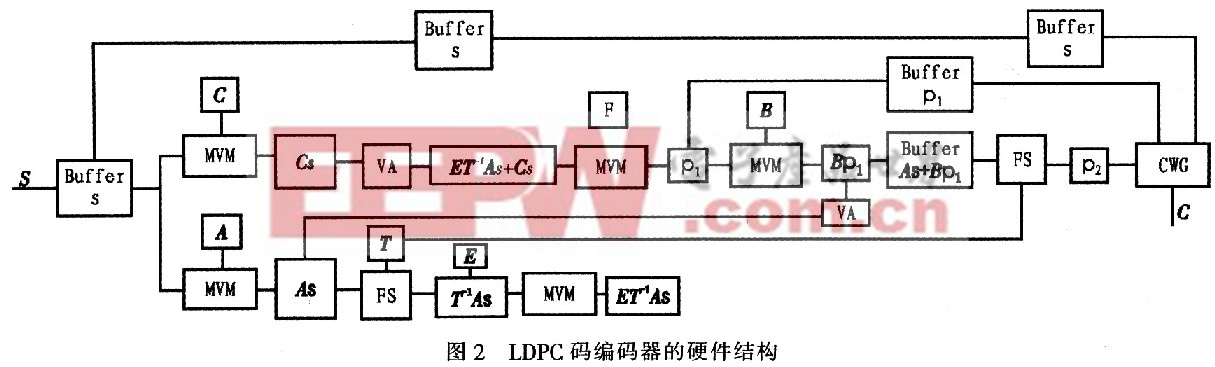

基于RU算法的LDPC编码实现过程主要是计算p1、p2的过程。设计编码器时,为了提高编码速度,将可以同时计算的步骤作并行处理,得到编码器的硬件结构如图2所示。

图2中,A、B、C、E分别代表图1中相应的矩阵,其中,F=-ET-1 B+D。从图2可知LDPC编码器主要由矩阵向量相乘(MVM)、前向迭代(FS)、向量相加(VA)和向量合成器(CWG)等运算单元以及存储各个矩阵相关信息的存储器组成。因为前向迭代运算基本上是矩阵与向量的乘法计算,所以矩阵向量乘法是LDPC编码过程最核心的单元。

3 矩阵向量乘法器(MVM)的实现

矩阵与矩阵的乘法运算以及前向迭代运算实质上都是矩阵与向量的乘法。下面说明矩阵向量乘法器硬件实现。

对于LDPC编码器,如何有效存储各个矩阵的信息是降低复杂度的关键。本文采用存储矩阵中元素‘1’在行中的位置以及对应行行重,如表1所示。例如矩阵X第3行的“1”元素,在行中的位置分别为“0”、“4”,该行的行重为2。由于LDPC编码过程中使用的矩阵大多是稀疏矩阵,所以采用该矩阵存储方案能比较有效地利用存储的空间并有利于矩阵与向量乘法的快速实现。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码