基于FPGA的语音信号LPC参数提取算法的实现

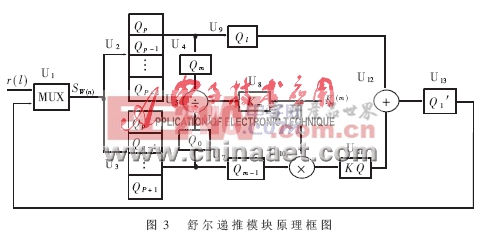

2.3 舒尔递推模块

舒尔递推算法一个很重要的特点是在整个递推过程中全部参与运算的量的初值、中间值和最终值皆小于1,因此特别适宜于采用定点运算的硬件系统来实现。该模块的设计也采用双RAM结构和同时取数同时运算的并行处理技术,所有运算单元的精度都是16位,每处理一次递推过程,就输出一个K(m)值。

舒尔递推模块的原理框图如图3所示。图中U2、U3为12×16bit的双口RAM;U4、U6、U7、U8、U9、U11、U13为数据寄存器;U5、U10、U12分别为16位的除法器、乘法器和加法器;U1为多路转换开关。该模块的工作过程是:当归一化自关函数r(l)通过U1送入U2和U3后,立即从中取出Qm和Q0送入除法器U5进行除运算,除得的结果送入U8;与此同时又分别从U2和U3中同时取出Ql和Qm-l,将Qm-l与Km在U10相乘后,送入U11,接着与Ql在U12进行相加,将结果经U13、U1重新送回U2和U3,接着又进行下一轮递推,该过程一直要进行到递推阶数完成。在每一次递推过程中,当U12在进行当前数据的加运算时,U10就可进行下一个数据的乘运算。这样整个过程就可在连续的流水线方式不间断地进行。

2.4 算术运算单元

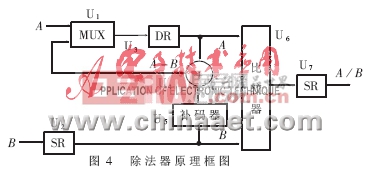

本系统所用到的算术运算单元有加法器、乘法器和除法器三种。加法器采用标准的全加器来构成,而乘法器则采用2的补码的BOOTH乘法器。下面介绍除法器的设计思想和工作原理。

由于本系统所使用的除法运算都是商小于1的除法,而且除法运算又比乘法运算少得多,因此对速度的影响也较小。综合考虑速度和资源占用两方面因素后,设计了下面的算法来实现除法器。设有两个数A和B,A是被除数,B是除数,现在求它们的商Q=A/B,Q1。现将Q表示成下列形式:

由于上述算法只需进行减法运算和除2运算,所以非常便于用硬件实现,据此算法设计的除法器原理框图如图4所示。图中U2为并入并出移位寄存器,每右移一位,实现一次除2操作;U5为补码器,它由反相器和加一电路构成,用于对B求补码;U7为串入并出移位寄存器;U6为比较器,用于对A、B两输入数进行比较,若A≥B,则输出“1”,否则输出“0”;U3为数据寄存器;U1为多路转换器;U4为加法器。该电路按下述原理工作:被除数A经U1送入U3并加到比较器U6的A端,除数B送入U2后右移一位再加到U6的B端。经U6比较后,若输出“1”,则先将U6的输出移入移位寄存器U7,再将A与B送入由U4和U5组成的减法器进行减法运算,所得差值再经U1送入U3;若输出为“0”,则仅将U6的输出移入U7即可。该步完成后,又将U2右移一位,再重复上述过程。整个操作一共要进行K次,最后U7中的数即为A/B的商。

在本系统中,将LPC分析与FPGA技术结合,充分利用了FPGA作为一种快速、高效的硬件平台在数字信号处理领域所具有的独特优势,实现了语音信号特征参数的快速提取,为语音信号的进一步处理打下基础。本系统采用50MHz的时钟频率进行工作。为考察其工作性能,对其整体性能指标进行了评估。由于影响整个系统速度的是乘法累加运算,因此它的工作性能也就决定了系统的性能。在求归一化自关函数r(l)过程中,涉及到近200次的乘积累加,采用并行处理技术和流水线操作方式的FPGA则可以用接近50MHz的数据速率进行工作,整个系统的性能同其他芯片相比约提高40%~60%,因此用FPGA技术来处理语音信号具有得天独厚的优点。

本系统除具有处理速度快的特点外,还具有独立灵活的输入输出接口及一组检测和控制信号线,可以方便地同任何一种处理器直接连接。由于FPGA自身所具有的抗干扰能力强、可靠性高的优点,本系统可广泛应用于自动控制、工业机器人、语音合成和语音编译码等领域,特别对嵌入式系统的设计具有重要意义。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码