基于FPGA的语音信号LPC参数提取算法的实现

2 系统设计

2.1 系统总体设计

由于语音信号具有短时平稳性,因此在进行处理时需进行分帧处理,然后逐帧对语音信号进行LPC分析。本系统中,语音信号S(n)的精度为12位,采样率为20k,帧长为10ms,相应于每帧有200个采样点,每帧提取的部分相关系数K(m)的阶数取为12。

对取出的每帧语音S(n)还需进行加窗处理,即用窗函数W(n)乘S(n),形成加窗语音信号SW(n)。为减小Gibbs效应的影响,本系统采用的窗函数为哈明窗。

为实现语音信号的LPC分析过程,选择FLEX10K系列中的EPF10K100器件作为目标芯片进行设计,因其具有独特的嵌入式阵列块EAB而特别适合于对数字信号进行处理[2-4]。系统设计中,采用自顶向下的设计思想,在顶层采用电路原理图的设计方法将系统分为几个功能模块,在底层则采用VHDL语言来实现各功能模块的设计。为保证系统整体的处理速度,电路设计采用了流水线作业方式,以数据流驱动各模块协调工作,同时在一些影响系统整体速度的环节采用了并行处理技术,很好地解决了制约系统速度的“瓶颈”。

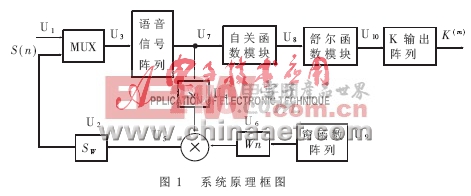

系统的原理框图如图1所示。图中U3、U10分别为由EAB构成的200×12bit和12×12bit的双口RAM阵列;U9为由EAB构成的200×12bit的ROM查找表,内置n=0~199的窗函数值W(n);U2、U4、U6为数据缓冲器;U7、U8分别为自关函数模块和舒尔递推算法模块;U1为多路转换开关;U5是12位乘法器。

系统工作原理如下:将一帧语音信号S(n)经U1送入U3,同时启动加窗过程,窗函数值W(n)通过查找ROM表U9获得,将取出的Wn和Sn送入乘法器U5相乘,乘积经U2和U1又送回U3,得到加窗语音信号SW(n),然后将SW(n)送入自关函数模块U7算出归一化自关函数r(n),再将r(n)送入舒尔递推模块求出部分相关系数K(m),存入U10。至此,一帧数据的LPC分析即告结束。

2.2 自关函数模块

自关函数的计算是影响系统速度的关键环节,它要进行大量的乘积累加操作。为提高系统运行速度,将加窗语音信号SW(n)同时存入两组RAM,采用并行取数的方式,同时取出参与运算的两个量,进行乘法运算,运算结果立即送入累加器进行累加。而此时乘法器又可进行下一对数据的乘积运算。整个过程中,乘法器和累加器一直在并行工作,从而保证了系统的流水线操作持续进行,最大限度地保证了系统的运行速度。

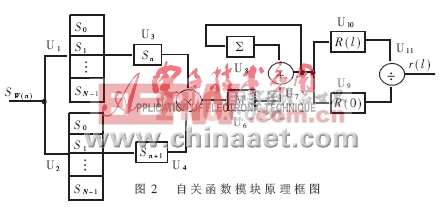

自关函数模块的原理框图如图2所示。图中U1、U2为EAB构成的200×12bit的双口RAM阵列;U8是带清零功能的数据寄存器,U7为加法器,它们二者共同构成累加器,为保证中间运算结果的精度,累加器的宽度为32位;U3、U4、U6、U9、U10为数据寄存器;U5为12位乘法器,乘积为24位;U11为32位除法器,商取16位。

该模块的工作过程是:将前面得到的加窗语音信号SW(n)同时存入U1和U2,然后按要求从中同时取出两乘数Sn和Sn+l送入乘法器U5进行乘运算,将乘积作为一个操作数同U8中的数进行累加。U8起始值被置为零,以后的值就是各次累加的和,最后一次累加的结果就是自关函数R(l)的值。然后再将它的值送入U10,将它同U9中的R(0)相除即得归一化的自关函数值r(l)。整个过程中,由于采用了并行处理技术,乘法器U5和累加器U7与U8一直处于工作状态,从而保证了系统的高速运行。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码