高清晰度数字电视传输系统设计与实现

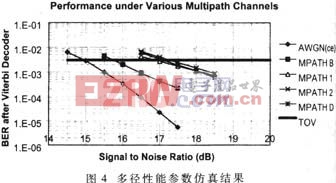

DMB-T系统中是在时域插入序列,利用信道的冲击响应来进行信道估计,对数据传输率的影响为7%。高斯噪声和时变信道对本信道估计算法的影响并不大,而且由于在开发设计过程中对算法进行了较多的优化与改进,所以本系统在抗多径干扰方面具有突出的性能,对移动接收环境尤其适用。对系统参数的仿真结果如图4所示。

3 系统同步性能仿真

为了评估系统的同步性能,设计了专门的同步电路,包括transmitter、Code acquisition、STR、AFC、FFT和Channel Estimation等部分,完整地实现了系统同步功能。仿真的交互式界面如图5所示。

图5中的Time ms 域示出的是实际系统运行的时间与仿真时间不同,下面各域表示频率偏移、时间偏移以及设计系统同步电路估计出来的频偏和时偏,在捕获同步序列后Code Acquisition Lock″域由红变绿,右半部分的域表示了信道估计之前和之后对应的星座图。从仿真可以得到整个码同步捕获时间仅仅需要5ms 这比同类系统的同步时间大大缩短,且时偏和频偏的纠正都达到了设计要求。

在DMB-T中同时利用了时域和频域的信息进。

采样时钟同步,利用扩频伪随机PN序列进行载波同步,信号的捕获时间缩短为5ms,并在20ms以内就能够完成时域和频域纠正,系统实现同步。

4 设计实现的流程

以往的设计流程中没有系统级仿真这一步,通常是在硬件完成以后才能进行修改和优化,而在系统级这个层次上进行的算法优化和参数调整不仅成本低,而且效率也很高。通过不断调整系统参数和改进相关算法得到最优性能和理论上的最优参数。从前面可以看出,采用SPW软件进行系统级设计与仿真可以让设计者把主要的精力放在系统的算法实现及优化上,而不必过多地考虑具体硬件实现。

当这些系统级仿真都全部完成以后,如图1的流程图所示,采用Cadence公司的硬件设计系统HDS、Verilog仿真软件Verilog-XL和NC-Verilog、SPW和Verilog协同仿真软件等把SPW中的系统级设计转换为RTL级的Verilog硬件描述语言,用FPGA实现、PCB布板进行验证。对FPGA实现的原型样机进行实地测试以后,可以把完整的设计做成专用集成电路ASIC。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码