基于3GHz CMOS低噪声放大器优化设计

4 电路仿真与版图设计

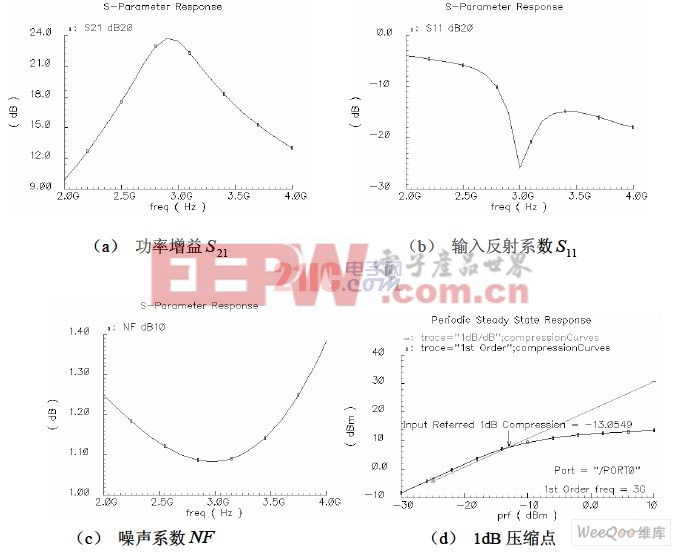

仿真采用TSMC的0.18 μm CMOS工艺,仿真环境为Cadence SpectreRF,电源电压为2V。仿真结果如图5所示。

从图5(a)可以看出,所设计低噪声放大器的功率增益在3 GHz处达到了23.4 dB,很好地满足了功率增益的要求。图5(b)中,输入反射系数S11达到-25.9 dB,显示了良好的输入阻抗匹配。图5(c)表明,经过噪声优化,电路的噪声系数只有1.1 dB,而图5(d)中的1dB压缩点为13.05 dBm,说明该低噪声放大器具有良好的线性度。

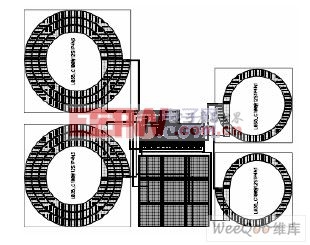

利用0.18 μm CMOS工艺模型,用cadence virtuoso软件对LNA进行版图设计,如图6所示,版图尺寸为0.485 mm × 0.395 mm。

5 结 论

本文通过对共源共栅结构的分析,从阻抗匹配、噪声系数和线性度的角度对电路的性能进行优化,设计出了一种3 GHz的低噪声放大器。在0.18 μm CMOS工艺下,利用Cadence SpectreRF软件对电路进行了仿真,结果显示,LNA的功率增益、阻抗匹配、噪声系数和线性度等参数都达到了良好的性能。最后对LNA进行了版图设计。

本文作者创新点:在分析共源共栅结构的基础上改进了LNA的电路结构,提出了在共源共栅结构之间加电感以改善噪声系数和并联电容以增加输入阻抗匹配的方法,对低噪声放大器的设计具有一定的参考价值。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码