基于3GHz CMOS低噪声放大器优化设计

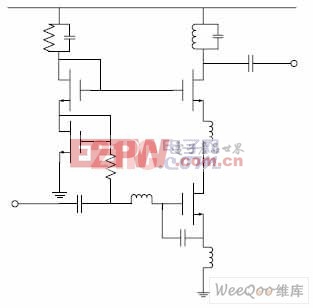

在上述结构的基础上加上偏置电路,并对电路结构进行优化调整,即可得到完整电路结构。本文所实现的电路结构如图2所示。

图2 LNA电路图

晶体管M1和M2构成Cascode结构,由于此结构没有考虑共源极和共栅极之间的匹配,所以在M1和M2之间加上电感Lm,可以提高两级间的匹配[7],这样不仅提高了功率增益,而且噪声系数也可以得到改善[8]。同时在M1的栅源之间并联一个电容C2,用来调节栅源之间的电容Cgs,方便与Lg和Ls一起来实现输入阻抗的匹配。

晶体管M3、M4和M1、M2共同组成共源共栅电流镜[9],作为偏置电路,且M3和M4的宽度相对应取较小的值,以减小偏置电路消耗的电流。电阻R2应取足够大以减小偏置电路带来的噪声电流,电阻R1用来调整输入晶体管M1的栅源电压和漏极电流以确定静态功耗,电容C1可以使得M2的栅极交流接电源电压。Cin与Cout均为隔直电容。

3 LNA性能优化

3.1 输入输出匹配

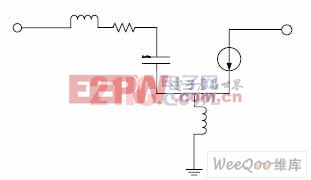

带源极负反馈的LNA输入端的小信号等效电路如图3所示,其中gm是M1的跨导,Cgs是M1的栅源电容Cgs1和C2并联得到的。

图3 源极负反馈结构的小信号等效电路

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码