基于FPGA的无线同播频率校准装置的设计

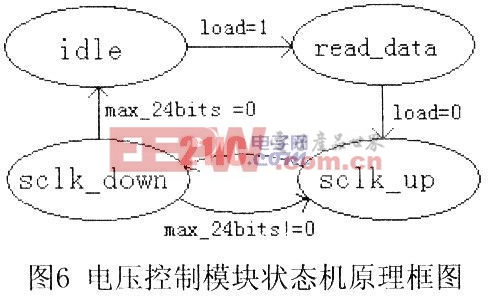

电压控制模块的状态机如图6所示,其工作方式是:

(1)idle状态时,ready输出赋为1,sclk赋为1,sync赋为1,max_24bits赋为24。

(2)当load=1时,状态转至idle,sync赋为0,data reg通过level和step引脚的值产生相应的控制帧。

(3)当load=0时,状态转至sclk_up,sclk赋为1,din赋为data_reg[max_24bits-1]。

(4)状态转至sclk down,sclk赋为0,max_24bits自减1。当max_24bits=0时,状态转至idle;否则状态转至sclk_up。

状态sclk_up和sclk_down的循环是用于产生控制DAC8552的时钟和数据,din通过max_24bits这个寄存器实现对data_reg从高到低逐位输出。

3 实验结果

3.1 软件仿真

利用Libero 8.0开发环境集成的Modelsim软件对电压控制模块设计进行仿真。模拟写入DAC8552的A、B通道数据为1010 1111 OO10 1011,十进制为44843,折算为电压值是2.258V。仿真时序图如图7所示,满足DAC8552接口的时序要求。

3.2 板上调试

将程序烧入FPGA运行,并通过频率计实际测量,测量结果如图8所示。由于频率计的精度只达到1Hz,测量的数据会有所偏差。考虑到校准后的频偏已经接近+0.05ppm(+0.64Hz),证明系统功能已经实现。但系统的效率不够高,需时过长,算法有待改善。

4 结束语

本设计通过FPGA、高精度DAC、压控恒温晶振和GPS信号接收模块,成功实现了同播系统发射设备的频率校准。除了同播系统,本设计还可应用于卫星信号同步、跳频通信的相关领域,发展空间十分广阔。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码