基于FPGA的无线同播频率校准装置的设计

1.3 分级控制方案

基于效率和精度的需要,本设计采用分级控制方案。GPS秒脉冲信号的精度误差为20ns,折算12.8MHz频率,最大频偏为20ppm。若以1秒作为时长比较脉冲数,调整的精度无法达到要求,同频干扰依然存在。由于秒脉冲信号的精度误差呈均匀分布,加长检测的时间可以提高信号精度,从而提高校准精度。但校准效率会下降,发射准备时间增加。另一方面,DAC的控制方式也影响系统的精度和效率。单次调整幅度大,效率高但精度低,幅度小则需时过长,所以不能以固定的幅度调整。根据VC-TCXO和DAC8552的参数,DAC最小的调整幅度为0.015Hz,DAC数值与VC-TCXO频率的关系是:

f(b)=12.8MHz+(b-b)×O.015Hz

式中f(b)是当前VC-TCXO频率,b是FPGA写入DAC的数值,b’是VC-TCXO输出12.8MHz时对应的DAC数值。VC-TCXO的电压可调范围是1.65±1.0V,折算b的有效范围为12 909~52 627。

为了平衡精度和效率的需要,系统采用了分级控制的方案。如表1所示,系统控制的逻辑分为五级。等级3的频偏和调整幅度最小,检测时间最长。脉冲数上下限用于固定时长内脉冲数的比较,判断是否需要调级。VC-TCXO的温度和老化的因素使晶体频率的上下限改变,所以等级1没有计数脉冲下限,等级5没有上限。FPGA根据当前的级别设定检测时间,再通过收到的脉冲数判断升级、降级或是调整电压值。

2 FPGA设计

2.1 FPGA顶层设计

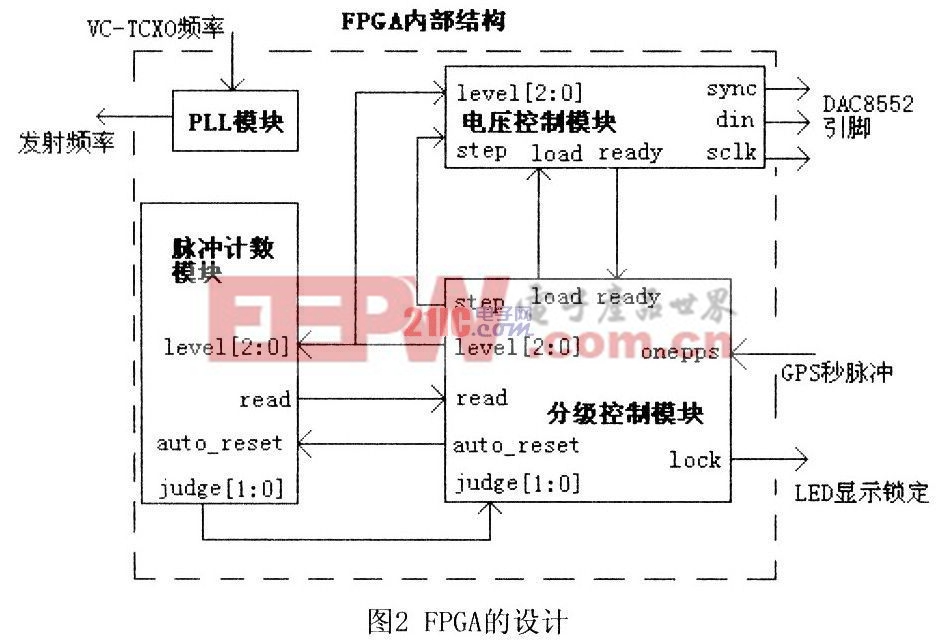

FPGA的设计采用自顶向下的设计方法,用Verilog HDL语言描述,在Actel公司的开发软件libero8.0中进行综合、优化、仿真和定时分析。顶层设计由PLL、分级控制、脉冲计数模块以及电压控制模块组成,如图2所示。

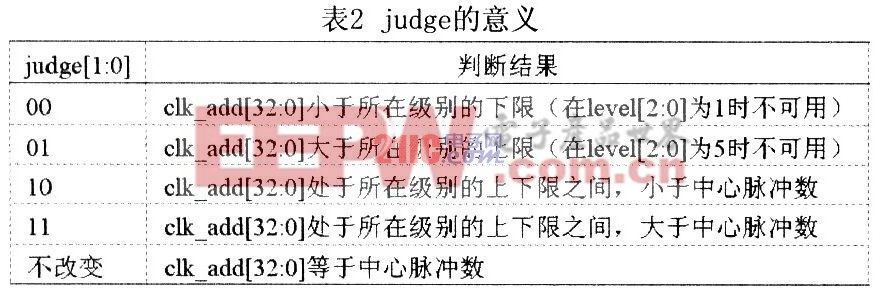

工作过程为:首先,初始化FPGA,电压控制模块将DAC8552的电压输出值置于中位(1.65V),分级控制模块的开始分级设定为3,并通过level[2∶0]连线将级别赋给脉冲计数模块和电压控制模块;分级控制模块收到GPS秒脉冲时,通过auto reset启动脉冲计数模块,收到read信号时读入judge[1∶0],judge[1∶0]的意义如表2所示。如果judge[1∶0]=00,level[2∶0]不为1,level[2∶0]降级;judge[1∶0]=01,level[2∶0]不为5,level[2∶0]升级;judge[1∶0]为10或11,通过step和load引脚调整电压控制模块。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码