多端口SDRAM控制器的设计与实现

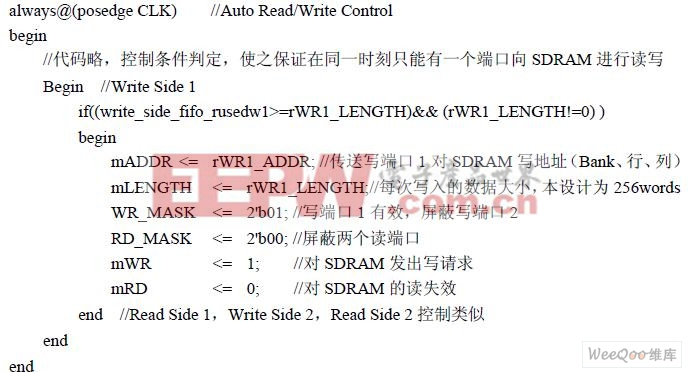

将数据采集模块得到的两组数据同时存贮到各自的写缓存FIFO 里,只要写缓存里的数据达到了SDRAM 每页的数据大小,就产生对SDRAM 的写请求,因为每个缓存的大小是两页SDRAM ,所以此时数据采集模块还可以继续存数据。类似的,VGA 所显示的数据也是从两个读缓存 FIFO 得到的,只要读缓存里的数据小于SDRAM 每页的数据,就产生对SDRAM 的读请求,这样每个缓存里的两页轮流操作。关键代码如下:

2.2 地址生成模块:

该模块用来自动生成对SDRAM进行存取操作的Bank地址,起始地址和突发长度。由于30位的像素数据等分各存入两个Bank里,所以在Bank里它们的对应地址是相同变化的,这样存取数据时,对两个Bank的读写地址的控制就是统一增减的,降低了使用一个Bank时读写控制的繁杂性。

2.3 自动刷新模块:

SDRAM需要不断的刷新操作,同一行的存储单元每隔64m s 需要刷新一次,对于本芯片的一个Bank 中的4096 行存储单元,则每15. 625us 就需要发出一个刷新命令,由于本设计采取缓存的办法,所以应该按读写SDRAM到缓存FIFO的时间为准来设计刷新计数器的初始值。以页模式进行读写,读数据的整个时间过程是tRCD+ tCL+mLENGTH ,写数据的整个时间过程是tRCD+mLENGTH ,其中tRCD是激活命令到读或写命令期间的延迟,tCL是读命令发出后到第一个有效数据之间的间隔,mLENGTH 是SDRAM 的页长,本设计中tRCD =3, tCL=3,mLength=256 。因此刷新计数器的初始值设置为2X(256+3+3)+ 2X(256+3)=1042 ,经计算远远小于所要求的刷新周期,初值设置合理。开始工作后,每当刷新计数器值减为0, 便会发出刷新命令,保证SDRAM内的数据不丢失,自动刷新之后直接进行预充电来关闭工作行。

2.4 命令产生模块:该模块主要负责命令仲裁、命令生成以及时序控制等。SDRAM 优先级仲裁算法通常有两种:一种是固定优先级算法,另一种是循环优先级算法。本文设计的SDRAM 控制器是应

用在实时图像处理系统中的,对数据处理效率要求很高,因此设计中选用固定优先级算法。本文规定优先级如下:初始化请求>刷新请求>读请求>写请求>其他。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码