多端口SDRAM控制器的设计与实现

1.2 SDRAM 的基本读写操作

读写操作主要完成与SDRAM 的数据交换。可以分为非突发连续操作模式和突发连续操作模式, 非突发指的是传送数据和地址必须是相对应一个一个的传输, 突发模式则是地址控制信号只需要给出首地址信息, 而数据实现连续传输过程, 突发数据的长度可以为1, 2,4, 8 和全页。

1.3 刷新操作

动态存储器都存在刷新问题。SDRAM 的刷新方式有自动刷新和自主刷新, 这里主要采用自动刷新方式, 每隔一段时间向SDRAM 发一条刷新命令。

2 基于FPGA 的多端口SDRAM 控制器设计

设计中选用的FPGA 是Altera 公司生产的CycloneII 系列中的EP2C35,选用的SDRAM 是ISSI 推出的64-MBIT 的IS42S16400B ,它是以1MWords X 16Bits X 4Banks 为组织结构的同步动态随机存储器,最高时钟频率可达143MHz[4]。

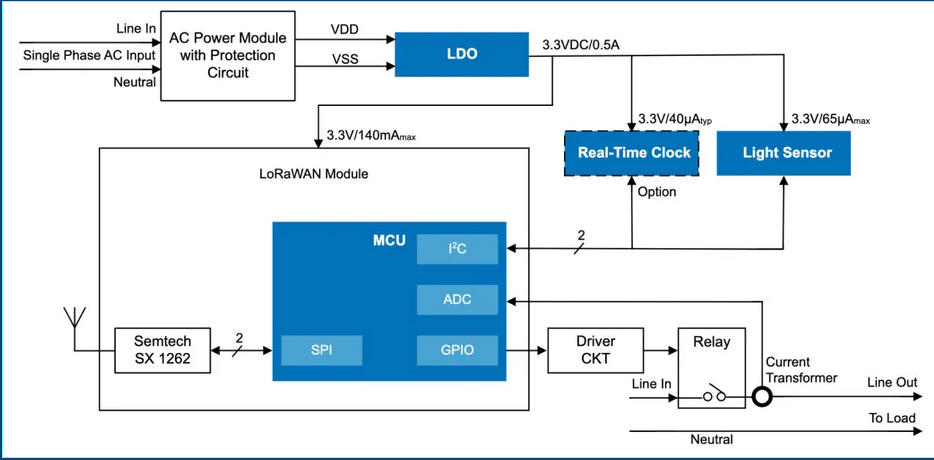

视频数据实时显示系统的基本构成如图1 所示[5]:

SDRAM 作为帧缓冲器,它的上一级数据输入是25MHz 的视频数据采集模块,所得到的数据经处理以后是每个像素点30 位数据,下一级是VGA 显示器以25MHz 的时钟进行数据输出,也要求是每个像素点30 位,而SDRAM 的数据宽度是16 位,因而每当存入和读取一个像素点的数据时,各需要进行两次传输。本款芯片SDRAM 的工作频率虽然可设置为100MHz ,但是如果不加缓存的话,就不能使用页突发模式来有效利用带宽,而且SDRAM 内部其他操作也需要占用一定的时间,不能达到实时显示的效果。本文在研究有关文献的基础上,利用FPGA 的片上资源开辟4 个FIFO 缓存,将SDRAM 的数据端口仿真成四个虚拟端口(两个写端口+两个读端口),每个端口的数据宽度都是16位,深度是两页SDRAM 的大小。且按照一致的规则将30 位采集和显示的数据分成两组与缓存进行存取,相应的,在SDRAM 上使用两个Bank 来分别存取每组数据。控制器根据缓存FIFO 的状态对SDRAM 发出读写请求,采用页模式突发传输和Bank 切换的方式来匹配时序要求。

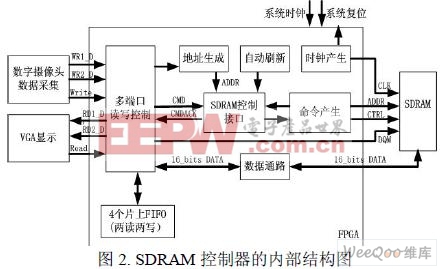

SDRAM 控制器的内部结构如图2 所示:

各功能模块描述如下:

2.1 多端口读写控制模块

该模块是与外设交换数据的接口,并且根据缓存FIFO 的状态,自动生成对SDRAM 的读写请求以及数据缓冲处理。它是本设计的核心。下面着重描述一下读写请求产生的设计过程和简要代码。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码