一种新型告诉浮点多DSP并行处理系统结构

2 多处理器系统基本结构

在多处理器系统中,处理器节点之间的通信通常使用两种方案:一种方案是使用专门的点对点通信信道;另一种方案是节点之间通过个共享的全局存储器和一条并行总线进行通信。这两种解决方案则构造了两种多DSP结构,即数据流式结构和簇式结构。

2.1 数据流工多处理器结构

2.2 族式多处理器结构

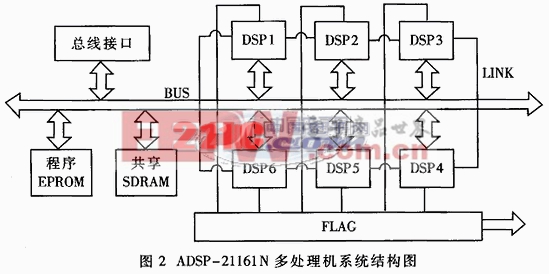

族式多处理器结构适合于需要一定灵活性的应用,特别是当一个系统必须我种不同任务,而其呈些可有需要并发运行的情况。簇式多处理器结构如1所示。

簇内存在一个瓶颈,这是因为在每个周期里只有两个处理器可以通过共享的总线进行通信,其它的处理器则被阻塞,直到总线被释放为止。由于ADSP-21161N也可以在一个族中进行点对点的链路口传送,该瓶颈很容易被消除。通过普通总线可以动态的建立和激活处理器间的数据链接。由于ADSP-21161N仅有两个链接口,各处理器间只能两两相连构成一条链路,不相邻的两个处理器节点之间的通信则要通过中间节点给予支持。但由于ADSP-21161N的链路口数据传输速率为100MB/s,而且传输字宽为8bit,基本可以消除此瓶颈的影响。

2.3 多处理器总线仲裁

多处理器系统中各ADSP-21161N之间的BR1-BR6要连在一起,用到的BRx线的数量等于系统中ADSP-21161N的数量。每个处理器驱动与自身ID2-0输入相对应的BRx管脚,并且监视其它处理器的BRx管脚。如果系统中的ADSP-21161N少于6片,未用的BRx管脚应上拉为高电平。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码