基于VHDL的Petri网系统的FPGA实现

3时延Petri网的实现

3.1时延Petri网的定义

时延PN被用来描述其运行与时间有关的系统。主要有两种:P时延PN和T时延PN。因二者是等效的,其中一个模型可以转换成另一个模型,故在此主要实现了T时延PN。

定义2[1]T时延PN是二元组

Tempo是从变迁集T到非负有理数集的函数,Tempo(Tj)=dj是与变迁Tj相联系的时限,它规定了Petri网中的每一个变迁的持续时间。

在T时延PN中,每个变迁均有一为零或任一正实数的持续时间。而库所中没有持续时间,只要和它相连的变迁激发,库所就可失去或获得托肯。当变迁的输入库所中含有托肯时,变迁是使能的,但要真正激发需要经过一段持续时间。

3.2变迁时化Petri网元件的实现

T时延PN中库所元件与同步Petri网一致。

T时延PN中变迁元件的实现是在基本Petri网中变迁元件的基础上设计了一个计时器TIME,如图2(b),clk为计时频率,决定了计时的精度;en为其使能端,当变迁可激发时,en为1,计时器开始计时,计时结束时co输出为1。

在图2(a)中变迁T与时延D=n相连,当库所P0和P1中各有一个托肯时,变迁T获得发生权,但到T发生,需有n个单位的延时.调用元件T_M和计时元件TIME,建立逻辑电路如图2(c)示,并经过编译形成图2(d)所示逻辑模块时化变迁元件tim。

用VHDL语言实现计时器模块源程序如下:

if clkevent and clk=1 then

if en=1 then

if q=n then q=0;co=1;else q=q+1; co=0;end if;

else q=0; co=0;end if;end if;

3.3变迁时化Petri网元件实现的应用举例

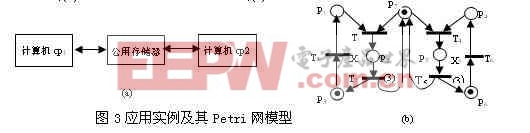

两台计算机使用一个公共存储器,如图3(a),假设每台计算机可以有三种状态:(a)不需要该存储器;(b)需要存储器但还没有使用它;(c)正在使用存储器。

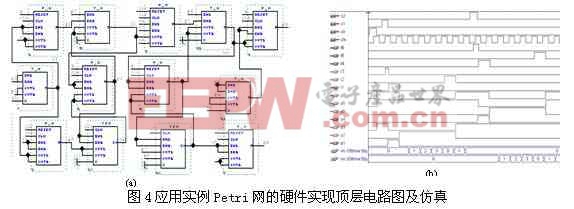

则对其建立Petri网模型如图3(b)示。各库所和变迁的含义解释为:P1,P4分别表示CP1、CP2发出需要该存储器请求;P2、P5分别表示CP1、CP2占用该存储器;P3,P6分别表示CP1、CP2不需要该存储器;P7表示存储器;变迁中与时间相关的是T2、T5,分别表示cp占用存储器的时间。这是一个时延Petri网系统。分别调用元件库中所形成的库所元件、变迁元件和时延变迁元件,作出该系统的逻辑电路图如图4(a),并在EDA软件Max+PlusⅡ中对其编译、仿真下载,仿真波形如图4(b)示。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码